Zostań Liderem Technologii Smart IoT

Cykl edukacyjny JM elektronik z Atmelem

Cz.4

SAM L21 - 32-bit Cortex-M0+ z poborem prądu od 35µA/MHz w trybie active

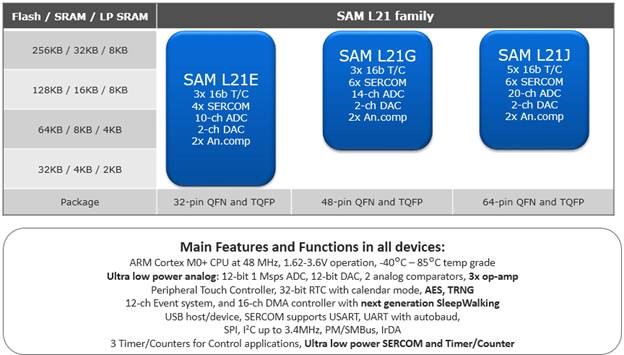

Rodzina mikrokontrolerów SAM L21 pracuje w oparciu o Cortex-M0+ i jest dedykowana do aplikacji zasilanych bateryjnie ze względu na bardzo niski pobór prądu (35µA/MHz w trybie Active, 900nA przy podtrzymaniu SRAM oraz z pracującym RTC, 200nA w głębokim uśpieniu) oraz bardzo niskie czasy wybudzeń ze stanów uśpienia. Wśród mechanizmów pozwalających na takie osiągi wymienić należy, podział na „power domain”, Sleepwalking, peryferia rozbudowane o funkcje picoPower oraz wiele innych. Zostaną one opisane w dalszej części tekstu.

SAM L21 dostępny jest w obudowach od 32-pin do 64-pin, maksymalna wielkość pamięci flash to 256KB oraz 40KB pamięci SRAM (z podziałem na 32KB SRAM, 8KB low power SRAM). Układy pracują z maksymalną częstotliwością 48MHz przy 2.46 CoreMark®/MHz. Cała rodzina została tak pomyślana, aby inżynier decydujących się na jej wykorzystanie miał szerokie opcje migracyjne, zarówno w ramach różnych wielkości pamięci jak i obudów.

Rys. 1. Podstawowe parametry SAM L21.

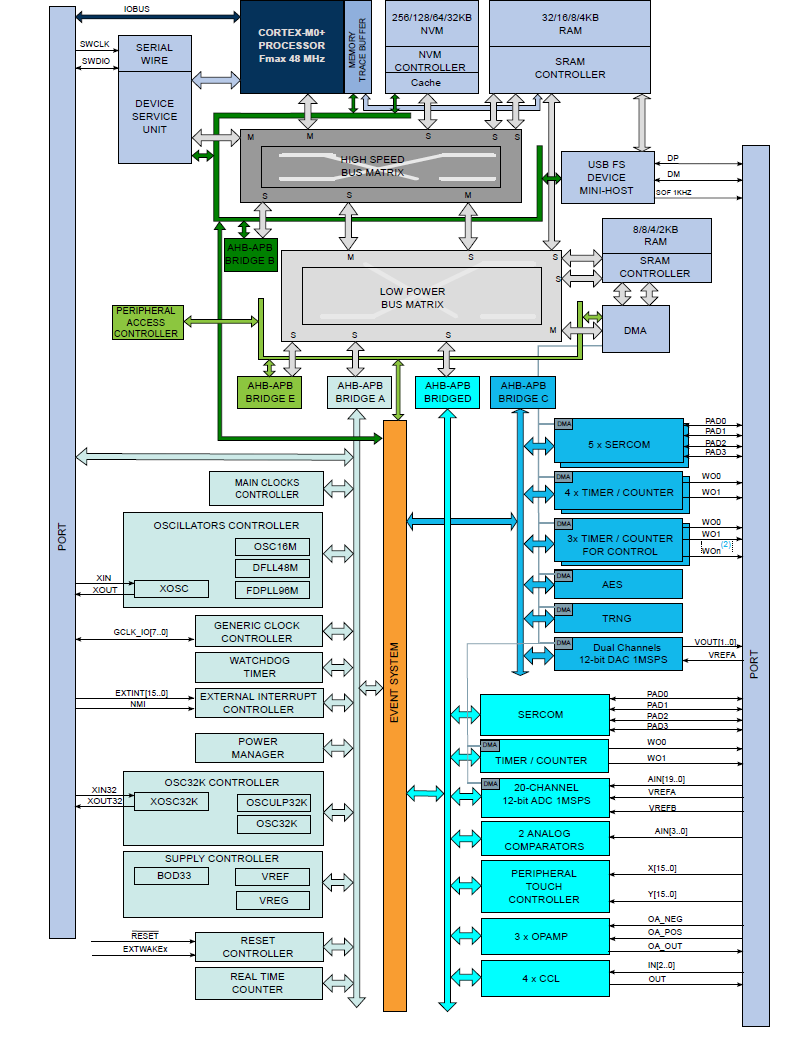

Rys. 2. Architektura rodziny SAML21.

W układach zaimplementowano szereg peryferiów znanych z rodziny SAM D, ale także pojawiły się zupełnie nowe rozwiązania. Ogromny nacisk położono na aspekty związane z poborem energii. Aby maksymalnie ograniczyć pobór prądu aplikacji należy pamiętać o kilku zasadach.

Zarządzanie energią

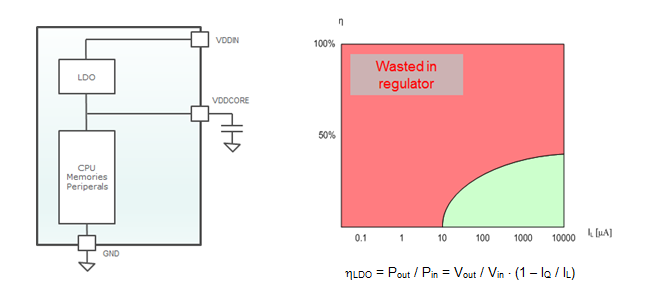

Część z tych zasad jest wymagana, aby wykorzystany mikrokontroler, sprzętowo wspierał pewne funkcjonalności. Pierwszym na to przykładem jest realizacja układu zasilania CPU, pamięci oraz peryferiów w mikrokontrolerze.

Rys. 3. Obwód dla standardowego mikrokontrolera obrazujący jak wiele energii może być tracone.

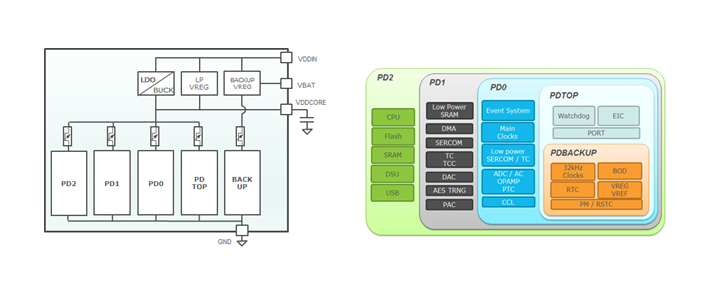

Na rysunku poniżej pokazano jak realizowane jest to w przypadku SAML21. W odróżnieniu od standardowego podejścia mamy tutaj kilka regulatorów, które zasilają różne power domain. Główny LDO został wzbogacony o możliwość regulacji napięcia w zależności od wymaganej częstotliwości pracy rdzenia oraz peryferiów. A podział na power domain pozwala na redukcję zużycia energii poprzez automatyczne wyłączanie zasilania poszczególnych PDx, w przypadku ich niewykorzystania oraz w trybach uśpienia. Same tryby uśpienia zostaną opisane w dalszej części.

Rys. 4. Zarządzanie energią przez SAM L21.

Budowa zegara

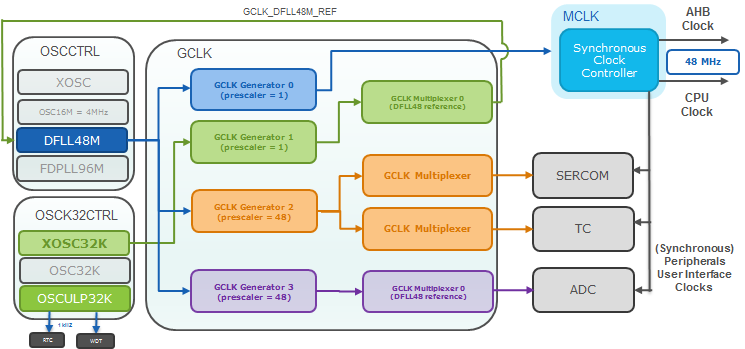

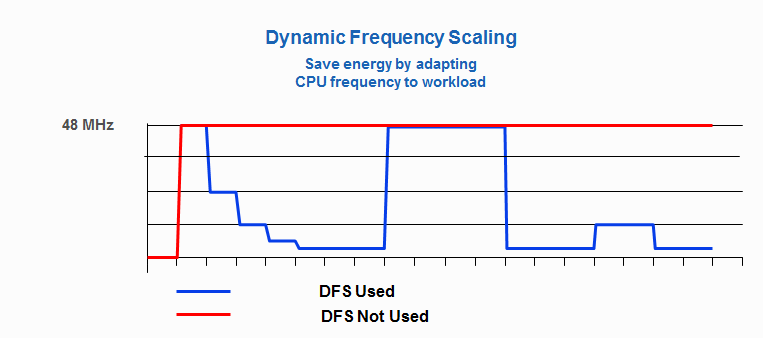

Kolejny element architektury, który został wykonany w nieco inny sposób to budowa systemu zegara. Znajduje się tu do dziewięciu generator/clock domain, które mogą być konfigurowane oraz przełączane niezależnie przez system bądź użytkownika. Pozwala to na dużą elastyczność taktowania poszczególnych peryferiów, zwłaszcza w stanach uśpienia. A sam CPU może pracować z różną częstotliwością w zależności od wymagań aplikacji (Dynamic Frequency Scaling).

Rys. 5. Budowa zegara w SAM L21.

Rys. 6. Dynamic Frequency Scaling.

Źródło taktowania może pracować także w trybie on-demand (flaga ONDEMAND). Oznacza to, że jest ono automatycznie zatrzymywane, w przypadku gdy nie jest ono potrzebne, a potem automatycznie włączane, gdy jego praca jest wymagana.

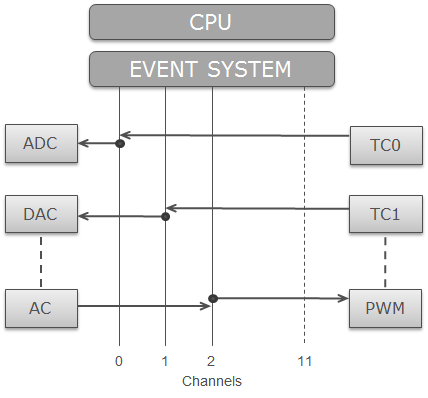

System eventów

Kolejnym elementem, który, odpowiednio wykorzystany może znacząco wpłynąć na sumaryczne zużycie energii jest system eventów. Wielu inżynierów zna go doskonale z układów serii Atxmega. Teraz został on zaimplementowany także w układach z Cortex-M0+.

Event system pozwala na współdziałanie peryferiów bez udziału CPU. Dodatkowo ma bardzo ciekawą właściwość. Otóż czas reakcji na event jest w 100% przewidywany. Poniżej graf obrazujący współdziałanie wybranych peryferiów bez udziału CPU.

Rys. 7. System eventów.

Stany uśpienia

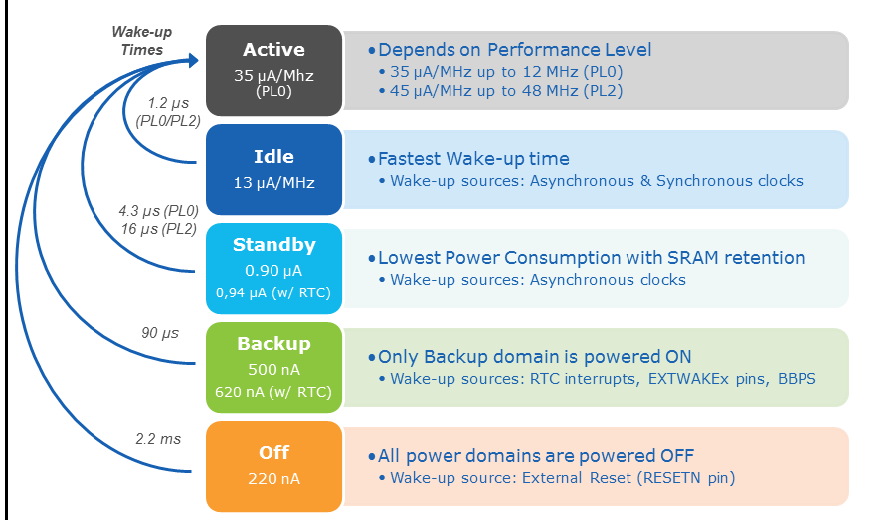

W ramach rodziny SAML21 wprowadzono możliwość wprowadzania mikrokontrolera w jeden z kilku stanów uśpienia. Poniższy graf przedstwia przybliżone pobory prądów oraz czasy wybudzeń do stanu aktywnego. Można odczytać także źródła, które są w stanie wybudzić układ z danego stanu uśpienia.

W trybie active CPU wykonuje kod, wszystkie zegary są dostępne, a pobór prądu zależy w dużej mierze od Performance Level (PL). SAML21 może pracować w jednym z dwóch performance level. Gdy pracuje w najniższym, czyli PL0, napięcie zasilania logiki jest redukowane, i jego poziom jest dostosowywany w zależności od częstoliwości pracy. W przypadku PL2 regulator napięcia dostarcza najwyższe możliwe napięcie, pozwalając na pracę z maksymalną częstotliowścią. Zmiany PLx można dokonywać w trakcie pracy mikrokontrolera. W trybie Idle zegar CPU jest wyłączony, różnie AHBx oraz APBx są wyłączone, ale mogą zostać uruchomione jeśli któreś z peryferiów będzie tego wymagać.

W trybie Standby wszystkie zegary, oprócz ULP32K sa wyłączone. Jednak peryferia mogą realizować swoje zadania, jesli w rejestrze konfiguracyjnym danego peryferia ustawiono flagę RUNSTDBY. Dodatkowo można tą pracę powiązać ze wcześniej wspomnianym ustawieniem flagi ONDEMAND, która decyduje o pracy źródła taktowania. W trybe Backupzasilana jest tylko domena BACKUP, do której, między innymi, należy RTC, BOD.

Rys. 8. Stany uśpienia.

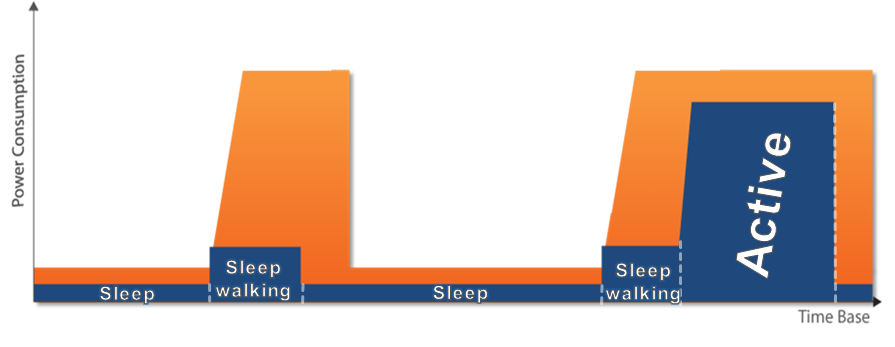

SleepWalking

Kolejną funkcjonalnością przeniesioną z AVR jest SleepWalking. Funkcjonalność ta daje możliwość, aby wybrane peryferia mogły wysłać żądanie wystawienia sygnału zegara, aby wykonać zadanie bez udziału CPU, w trybie Standby. W przypadku SAML21 zostało to wzbogacone o współpracę z power domain. Oznacza to, że zasilanie do danej power domain będzie dostarczone, gdy któryś z elementów tego potrzebuje do pracy. Kiedy zadanie jest wykonane, mikrokontroler może zostać wybudzony do stanu aktywnego, bądź tez pozostać w Standby, tak jak pokazuje to poniższy rysunek.

Rys. 9. SleepWalking

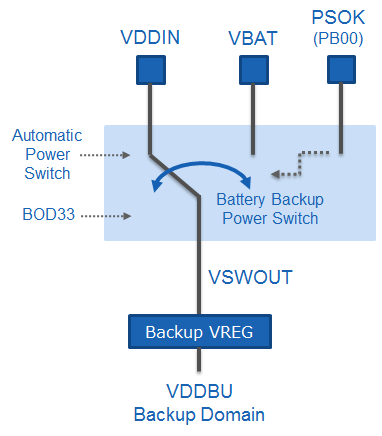

Zasilanie bateryjne

SAML21, jak wspomniano na początku, został zaprojektowany tak, aby mógł pracować w aplikacjach, gdzie zasilanie, z reguły, jest bateryjne. Dlatego też wyposażony został w szereg funkcjonalności wspomagających inżyniera w procesie optymalizacji zużycia energii, które zostały opisane powyżej. Dodatkowo układ posiada Battery Backup Power Switch (BBPS). Jest to automatyczny przełącznik źródła zasilania, pomiędzy baterią (VBAT) a głównym zasilaniem (VDDIN). Przełączenie na zasilanie bateryjne odbywa się gdy napięcie zasilania spadnie poniżej 1.75 V lub poniżej progu BOD33. Układ wraca do zasilani głównego gdy napięcie wzrośnie do 1,85V lub zostanie to wymuszone poprzez pin PSOK (Main Power Supply OK).

Rys. 10. Battery Backup Power Switch.

Peryferia SAM L21

• Do sześciu Serial Communication Interfaces (SERCOM), w tym jeden low-power SERCOM. Każdy z nich można skonfigurować jako: USART, I2C do 3.4MHz, SPI, LIN slave

AES (Advanced Encryption Standard)

Zwracamy również uwagę na moduł AES (Advanced Encryption Standard), który poza standardowymi funkcjami, został zabezpieczony przed atakiem polegającym na analizie poboru prądu. Domyślnie wszystkie cztery poniższe tryby są włączone (można wyłączyć jeden lub kilka z trybów):

Wsparcie

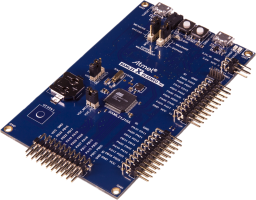

Wraz z nową rodziną w ofercie pojawił się zestaw ewaluacyjny ATSAML21-XPRO-B.

Cała rodzina SAML21 wspierana jest przez bezpłatne środowisko Atmel Studio 6 oraz Atmel Software Framework (ASF). Znaleźć tam można setki przykładowych programów, a także sterowniki peryferiów.

A tutaj przykład zasilania SAML21 energią dłoni:

Cykl edukacyjny „Lider Technologii Smart IoT” JM elektronik z Atmelem

Z pomocą specjalistów producenta – firmy Atmel – oraz oficjalnego dystrybutora Atmel na Polskę –JM elektronik – można stać się ekspertem technologii inteligentnych, tak szybko rozpowszechniających się obecnie na rynku elektroniki. Cykl artykułów, webinariów i warsztatów pokaże bogactwo układów opartych o rdzeń Cortex-M0+ oraz Cortex-M7, dedykowanych dla rynku tzw. Internetu Rzeczy, czyli Internet Of Things (IoT).

Cykl „Lider Technologii Smart IoT” rozpoczyna szereg publikacji:

Nie przegap kolejnych artykułów!

Osoby zainteresowane śledzeniem kolejnych artykułów edukacyjnych oraz następujących po nich webinariów proszone są o zgłoszenie się do listy subskrypcyjnej cyklu pod adres marketing@jm.pl z dopiskiem: Cykl edukacyjny „Lider Technologii Smart IoT”.