### **Features**

- $V_{IN}$  input range from 7.5V to 36V

- Individual cell voltage monitor outputs 1/2 of battery cell voltage, when the analog output is 2.1V, it has an accuracy of ±7.5mV

- Internal cell charging balance switches

- Integrated voltage regulator with 5V/50mA and  $\pm 1\%$  accuracy

- At Ta=-40°C~85°C, 2.5V reference voltage output with a maximum variation of 15mV in temperature drift

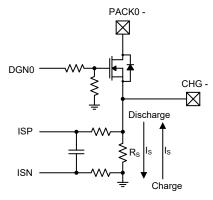

- Two Discharge N-type MOSFET gate drivers

- Single Charge N-type MOSFET gate driver

- Charge/Discharge differential current monitor:

- IMON pin outputs amplified ISP0-ISN0 differential voltage

- Voltage amplifying rate selection: 10/50

- Discharge short-current detection:

- Detection threshold voltage selection: 50mV/ 100mV/150mV/200mV/250mV/300mV/350mV/ 400mV

- Detection debounce time selection: 0µs~992µs, 32 sections, 32µs per section

- Integrated Over-temperature protection selection: 85°C/100°C/125°C/150°C

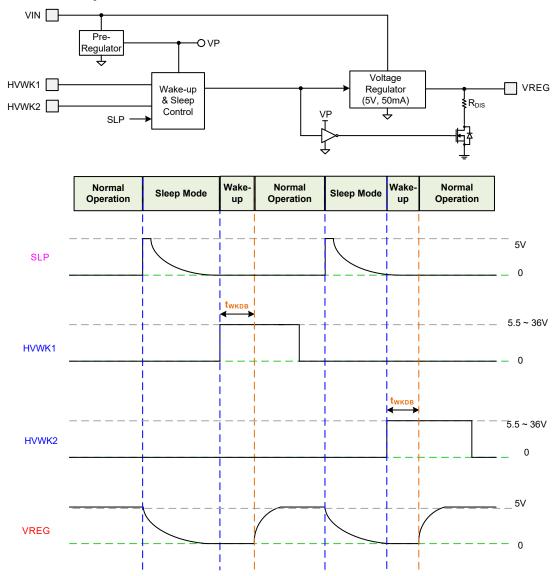

- Sleep mode with  $0.1\mu A$  ultra-low standby current

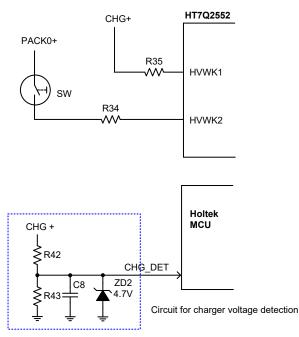

- Two High-voltage wake-up functions

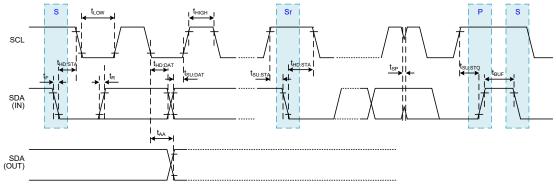

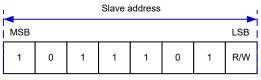

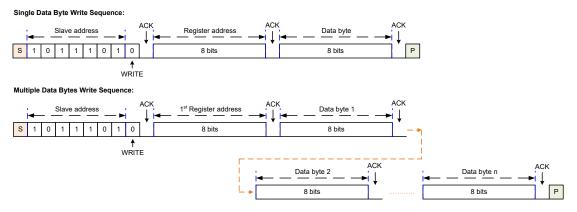

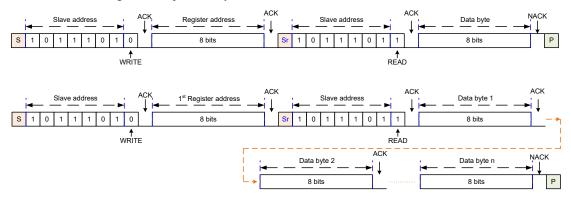

- I<sup>2</sup>C bus communication with host MCU

- Operating temperature range: -40°C to +85°C

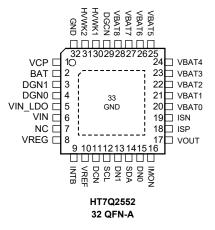

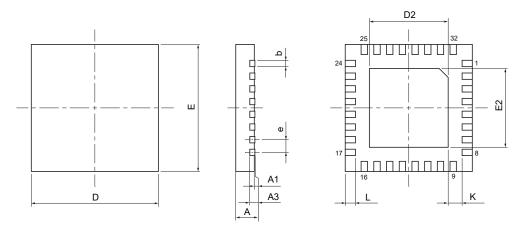

- Package type: 32-pin QFN

## Applications

- Handheld vacuum cleaners

- Electric power tools

## **General Description**

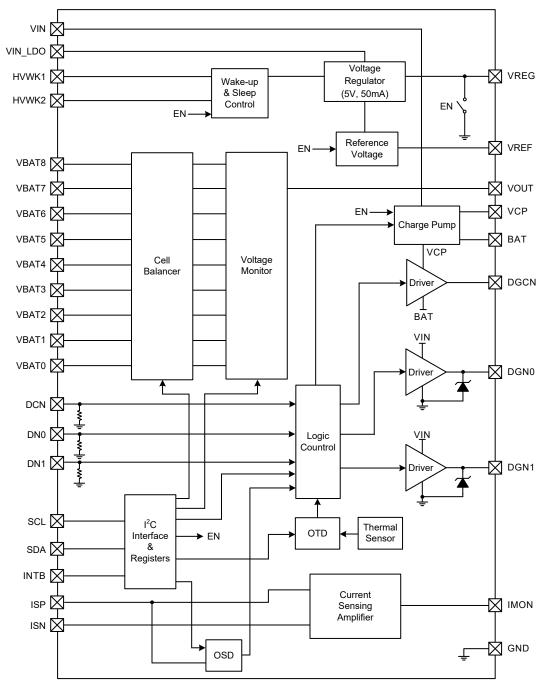

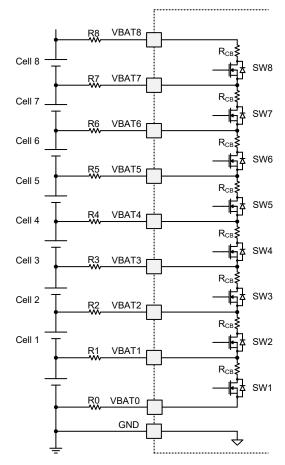

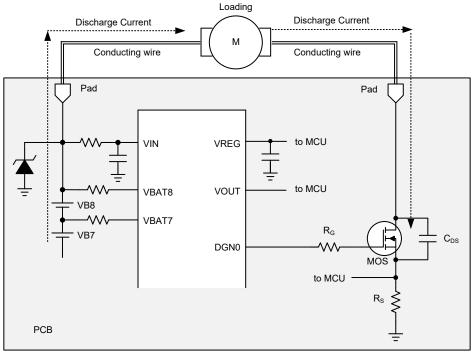

The HT7Q2552 is a high voltage analog-front-end IC for 3 to 8 cell Li-ion rechargeable battery protection. It consists of a 5V high accuracy regulator, an accuracy 2.5V reference voltage output, an individual cell voltage monitor, two discharge paths, i.e., low-side power switch gate drivers, a charge path, i.e., high-side power switch gate driver, a charge/ discharge differential current monitor, and a discharge short-current protection. The cell voltage monitor is designed to monitor each battery cell voltage individually and outputs the divide-by-2 voltage to the analog multiplexer with  $\pm 0.36\%$  accuracy. The current monitor channel provide charge and discharge current monitoring and short-current protection. The device can directly drive external N-type MOSFETs to control charge and discharge by charge and discharge gate drivers. The internal battery balance circuitry provides a cell balance current without the need of external transistors. Each monitored battery cell voltage can be observed sequentially from VBAT1 to VBAT8 which benefits MCUs with a lower number of ADCs.

An integrated 5V regulator provides a 5V supply to the MCU with a 50mA driving current capability and which has  $\pm 1\%$  accuracy. The voltage regulator, cell voltage monitor, current monitors, and gate drivers are shut down with an ultra-low standby current 0.1µA when the device is in the Sleep mode. When the HVWK1 or HVWK2 pin is triggered by a voltage greater than its threshold, the device will return to the normal operating status.

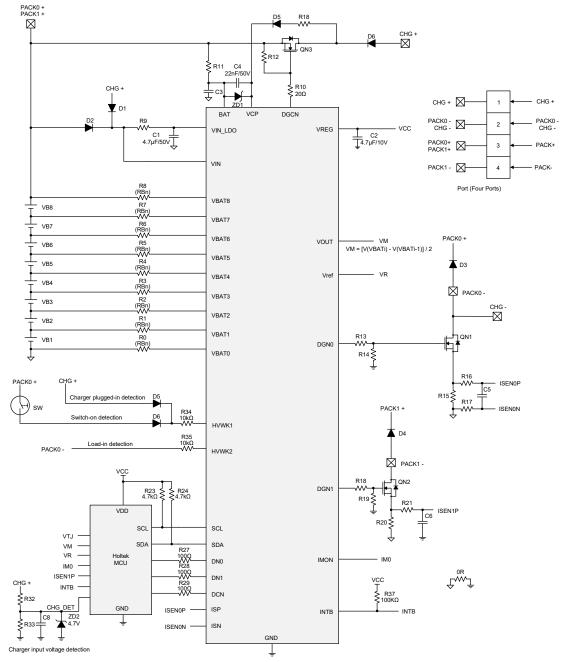

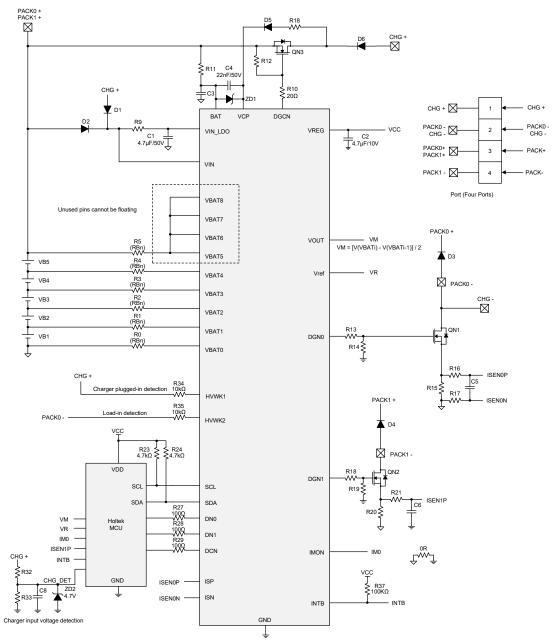

## **Functional Block Diagram**

## **Pin Assignment**

# **Pin Description**

| Pin No. | Name    | Туре | Pin Description                                                                                                                                     |

|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCP     | 0    | Charge pump capacitor for DGCN. Connect a capacitor between VCP and BAT                                                                             |

| 2       | BAT     | 0    | Charge pump capacitor for DGCN. Connect a capacitor between VCP and BAT                                                                             |

| 3       | DGN1    | 0    | Gate driver output 1 for driving discharge n-MOSFET.<br>Recommended for applying on secondary loading path.                                         |

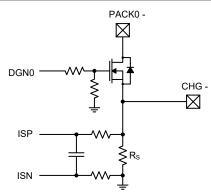

| 4       | DGN0    | 0    | Gate driver output 0 for driving discharge n-MOSFET.<br>Recommended for applying on primary loading path.                                           |

| 5       | VIN_LDO | Р    | Input supply voltage for regulator                                                                                                                  |

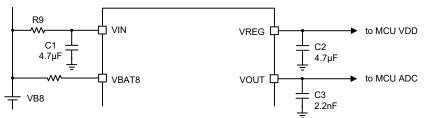

| 6       | VIN     | Р    | Input supply voltage for gate drivers                                                                                                               |

| 7       | NC      | _    | Not connected                                                                                                                                       |

| 8       | VREG    | 0    | Regulator 5V/50mA output. Connect 4.7µF capacitor typically                                                                                         |

| 9       | INTB    | 0    | Interrupt output pin of short current detection for MCU. NMOS open drain output and output an 'L' level pulse when short-current event is detected. |

| 10      | VREF    | 0    | Reference voltage 2.5V output pin                                                                                                                   |

| 11      | DCN     | Ι    | Gate driver DGCN control input*                                                                                                                     |

| 12      | SCL     | I/O  | I²C serial clock line                                                                                                                               |

| 13      | DN1     | Ι    | Gate driver DGN1 control input*                                                                                                                     |

| 14      | SDA     | I/O  | I <sup>2</sup> C data clock line                                                                                                                    |

| 15      | DN0     | I    | Gate driver DGN0 control input*                                                                                                                     |

| 16      | IMON    | 0    | Current monitor output pin. Voltage of ISP-ISN multiplied by 10 or 50 is outputted.                                                                 |

| 17      | VOUT    | 0    | Voltage monitor output                                                                                                                              |

| 18      | ISP     | I    | Current monitor positive terminal voltage input pin. The voltage level of ISP pin should be higher than that of ISN in discharge state.             |

| 19      | ISN     | I    | Current monitor negative terminal voltage input pin. Connected to the most negative terminal of battery cells.                                      |

| 20      | VBAT0   | Ι    | Battery cell 1 negative terminal                                                                                                                    |

| 21      | VBAT1   | I    | Battery cell 1 positive terminal and battery cell 2 negative terminal                                                                               |

| 22      | VBAT2   | Ι    | Battery cell 2 positive terminal and battery cell 3 negative terminal                                                                               |

| 23      | VBAT3   | I    | Battery cell 3 positive terminal and battery cell 4 negative terminal                                                                               |

| 24      | VBAT4   | I    | Battery cell 4 positive terminal and battery cell 5 negative terminal                                                                               |

| 25      | VBAT5   | I    | Battery cell 5 positive terminal and battery cell 6 negative terminal                                                                               |

| 26      | VBAT6   | I    | Battery cell 6 positive terminal and battery cell 7 negative terminal                                                                               |

| 27      | VBAT7   | Ι    | Battery cell 7 positive terminal and battery cell 8 negative terminal                                                                               |

| Pin No. | Name  | Туре | Pin Description                                           |

|---------|-------|------|-----------------------------------------------------------|

| 28      | VBAT8 | I    | Battery cell 8 positive terminal                          |

| 29      | DGCN  | 0    | Gate driver output for driving charge n-MOSFET            |

| 30      | HVWK1 | I    | Sense and trigger pin of High voltage Wake-up function 1. |

| 31      | HVWK2 | I    | Sense and trigger pin of High voltage Wake-up function 2. |

| 32      | GND   | G    | Ground terminal                                           |

| EP      | GND   | G    | Connected to GND                                          |

Note: I: Input; O: Output; P: Power; G: Ground; \*: Internal pull down with  $370k\Omega$ .

## **Absolute Maximum Ratings**

| Pin/Paramete                                          | r                    | Value        | Unit |

|-------------------------------------------------------|----------------------|--------------|------|

| VIN, VIN_LDO, HVWK1, HVWK2, BAT                       |                      | -0.3 to +48  | V    |

| DGCN, VCP                                             | -0.3 to +60.0        | V            |      |

| VREG                                                  | -0.3 to +5.5         | V            |      |

| DGN0, DGN1                                            |                      | -0.3 to 18   | V    |

| VOUT, SCL, SDA, DN0, DN1, DCN, ISP, ISN, IM           | ON, INTB, VREF       | -0.3 to +5.5 | V    |

| ∆[VBATi~VBAT(i-1)], i=8, 7, 6, 5, 4, 3, 2, 1          | 3, 2, 1 -0.3 to +5.5 |              |      |

| Operating Temperature Range                           |                      | -40 to +85   | °C   |

| Maximum Junction Temperature                          |                      | +125         | °C   |

| Storage Temperature Range                             |                      | -60 to +150  | °C   |

| Lead Temperature (Soldering 10sec)                    |                      | +260         | °C   |

| ESD Susceptibility                                    | Human Body Model     | ±2000        | V    |

|                                                       | Machine Model        | ±200         | V    |

| Junction-to-Ambient Thermal Resistance, $\theta_{JA}$ | 32QFN (4×4)          | 47           | °C/W |

# **Recommended Operating Range**

| Pin / Parameter | Value      | Unit |

|-----------------|------------|------|

| Vin             | 7.5 to 36  | V    |

| TA              | -40 to +85 | °C   |

Note that Absolute Maximum Ratings indicate limitations beyond which damage to the device may occur. Recommended Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specified performance limits.

## **Electrical Characteristics**

| Symbol                                                                      | Parameter                                                                   | Test Condition                                                                                                                                                              | Min.  | Тур.  | Max.   | Unit       |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|------------|

| Supply and In                                                               |                                                                             | Test condition                                                                                                                                                              |       | тур.  | IVIAA. | Unit       |

|                                                                             | Supply Voltage                                                              |                                                                                                                                                                             | 7.5   |       | 36.0   | V          |

| I <sub>IN(STB)</sub>                                                        | Supply Current (Standby)                                                    | EN_S=EN_VREF=IMCE=ISCE='0'<br>EN_OTD=EN_TS='0'<br>DN0=DN1=DCN='0'                                                                                                           |       | 3.5   | 6.0    | μΑ         |

| I <sub>IN(STB_DSG)</sub>                                                    | VIN Supply Current with DGN0<br>and Short Current Detection is<br>Activated | EN_S=EN_VREF=IMCE=<br>EN_OTD=EN_TS='0'<br>ISCE='1', DN0='1', DN1=DCN='0'                                                                                                    |       | 18    | 20     | μA         |

| IOPR_DGNx                                                                   | VIN Operating Current when<br>DGN0 and DGN1 Outputs are On                  | DN0=DN1='1', DCN='0'                                                                                                                                                        | _     | 15    | _      | μA         |

| I <sub>SLP</sub>                                                            | Standby Current in SLEEP Mode                                               | SLP1='0', SLP0='1', V <sub>HVWK</sub> =0V                                                                                                                                   | _     | 0.1   | 0.2    | μA         |

| Voltage Regul                                                               | lator                                                                       |                                                                                                                                                                             |       |       |        |            |

| V <sub>REG</sub>                                                            | Regulator Output Voltage                                                    | I <sub>LOAD</sub> =10mA                                                                                                                                                     | 4.95  | 5.00  | 5.05   | V          |

| I <sub>REG</sub>                                                            | Regulator Maximum Output<br>Current                                         | V <sub>IN</sub> =7.5V, T <sub>A</sub> =-40~85°C                                                                                                                             | 50    | _     | _      | mA         |

| $\Delta V_{\text{REG}}$                                                     | Load Regulation                                                             | ILOAD=0~50mA                                                                                                                                                                | —     | —     | 50     | mV         |

| $rac{\Delta V_{\text{REG}}}{(V_{\text{REG}} \times \Delta V_{\text{IN}})}$ | Line Regulation                                                             | V <sub>IN</sub> =7.5~36V, I <sub>LOAD</sub> =10mA                                                                                                                           | _     | 0.02  | _      | %/V        |

| $\frac{\Delta V_{\text{REG}}}{(V_{\text{REG}} \times \Delta T_{\text{A}})}$ | V <sub>REG</sub> Temperature Coefficient                                    | I <sub>LOAD</sub> =1mA, T <sub>A</sub> =-40~85°C                                                                                                                            | _     | ±100  | _      | ppm/<br>°C |

| R <sub>DIS</sub>                                                            | V <sub>REG</sub> Discharge Resistance                                       | SLP1='0', SLP0='1', V <sub>REG</sub> =1V,<br>I <sub>REG1</sub> denotes VREG input current at<br>V <sub>REG</sub> =1V, R <sub>DIS</sub> =V <sub>REG</sub> /I <sub>REG1</sub> |       | 330   | _      | Ω          |

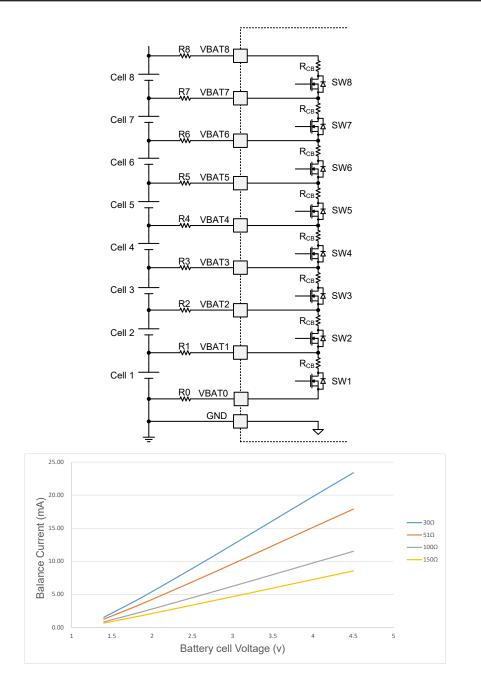

| Cell Balancer                                                               | 1                                                                           | 1                                                                                                                                                                           |       |       |        |            |

| D                                                                           |                                                                             | V <sub>Bi</sub> =4.5V (i=1~8),<br>VBATi series resistors=0Ω                                                                                                                 | 80    | 110   | 140    | Ω          |

| Rcb                                                                         | Cell Balance Resistance                                                     | V <sub>Bi</sub> =2.5V (i=1~8),<br>VBATi series resistors=0Ω                                                                                                                 | 120   | 160   | 200    | Ω          |

| Reference Vol                                                               | Itage                                                                       |                                                                                                                                                                             |       |       |        |            |

| V <sub>REF</sub>                                                            | Reference Voltage                                                           | EN_VREF='1'                                                                                                                                                                 | 2.492 | 2.500 | 2.508  | V          |

| $\Delta V_{\text{REF}}$ (Note)                                              | V <sub>REF</sub> Temperature Coefficient                                    | I <sub>LOAD</sub> =1μΑ, Τ <sub>A</sub> =-40~85°C                                                                                                                            | —     | —     | ±15    | mV         |

| IREF_SOUR                                                                   | V <sub>REF</sub> Pin Output Source Current                                  | CVREF=0.1µF. Peak current at<br>EN_VREF '0'→'1' rising edge                                                                                                                 | _     | 2     | _      | mA         |

| IREF_SINK                                                                   | VREF Pin Output Sink Current                                                | CVREF=0.1µF. Peak current at<br>EN_VREF '1'→'0' falling edge                                                                                                                | _     | 1     | _      | mA         |

| $t_{S}V_{REF}$                                                              | V <sub>REF</sub> Pin Settling Time                                          | Settling time from $V_{REF}=0V$ to 2.475V. $C_{VREF}=30pF$                                                                                                                  | _     | 20    | 30     | μs         |

| Input/Output I                                                              | Logic                                                                       | ~                                                                                                                                                                           |       |       |        |            |

| VIL                                                                         | DN0, DN1, DCN Input Logic Low voltage                                       | _                                                                                                                                                                           | _     | _     | 1.5    | V          |

| VIH                                                                         | DN0, DN1, DCN Input Logic High<br>Holtage                                   | _                                                                                                                                                                           | 3.5   | _     | _      | V          |

| R <sub>PD</sub>                                                             | DN0, DN1, DCN Pull Down<br>Resistance                                       | _                                                                                                                                                                           | _     | 370   | _      | kΩ         |

| V <sub>L(INTB)</sub>                                                        | INTB 'Low' Output Voltage                                                   | Load current=500µA, V <sub>REG</sub> =5V                                                                                                                                    | _     | —     | 0.1    | V          |

| R <sub>PU_INTB</sub>                                                        | INTB Pulled High to VREG<br>Resistance                                      |                                                                                                                                                                             | _     | 50    | _      | kΩ         |

| High Voltage                                                                | Wake-Up                                                                     | I.                                                                                                                                                                          |       | 1     | 1      |            |

| Vwkth                                                                       | HVWK1 and HVWK2 Threshold<br>Voltage                                        | _                                                                                                                                                                           | _     | 5.5   | _      | V          |

| Symbol | Parameter                        | Test Condition         | Min. | Тур. | Max. | Unit |

|--------|----------------------------------|------------------------|------|------|------|------|

| Тиков  | HVWK1 and HVWK2 Debounce<br>Time | —                      | 1    | —    | _    | ms   |

| Іwк    | HVWK1 and HVWK2 Input<br>Current | V <sub>HVWK</sub> =36V |      | 50   | _    | μA   |

Note: Design guaranteed.

# **Electrical Characteristics (Cont.)**

| Symbol                | Parameter                                                           | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Min.                | Тур.                 | Max.                | Unit |

|-----------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|---------------------|------|

| Cell Volta            | age Monitor                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |                      |                     |      |

| V <sub>Bi</sub>       | Cell Voltage                                                        | i=1~8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5                 | _                    | 4.5                 | V    |

| V <sub>B(MIN)</sub>   | Input Voltage between VBATi and VBATi-1 for Cell Voltage Monitoring | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                   | 1.5                  | _                   | V    |

| I <sub>Bi(PWR)</sub>  | Cell Input Leakage Current<br>when VIN Powered                      | V <sub>Bi</sub> =5V (i=1~8). EN_S='0'. V <sub>IN</sub> =V <sub>BAT8</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -0.1                | _                    | 0.1                 | μA   |

| I <sub>Bi(ACT)</sub>  | Cell Input Current when Voltage<br>Monitoring                       | V <sub>Bi</sub> =4.2V×i. EN_S bit='1', V <sub>IN</sub> =36V.<br>i=1∼8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                   | 15                   | _                   | μA   |

| Vout_vm               | Cell Voltage Monitor Output<br>Accuracy                             | V <sub>Bi</sub> - V <sub>Bi-1</sub> =4.2V. i=1~8. T <sub>A</sub> =25°C<br>V <sub>Bi</sub> - V <sub>Bi-1</sub> =4.2V. i=1~8. T <sub>A</sub> =-40~85°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.094<br>2.092      | 2.100                | 2.106<br>2.108      | V    |

| Ivout_sour            | Cell Voltage Monitor Output Source<br>Current                       | $\begin{array}{l} V_{Bi} - V_{Bi-1} - 4.2V, \ i=1\mathcase 0.1 \ A_{A} - 40\mathcase 0.1 \ A_{A} - 40\mathc$ |                     | 2.100                |                     | mA   |

| Ivout_sink            | Cell Voltage Monitor Output Sink<br>Current                         | $V_{Bi} - V_{Bi-1}$ =4.2V. i=1~8. C <sub>VOUT</sub> =0.1µF.<br>Peak current at EN_S '1'→'0' falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | 1                    | _                   | mA   |

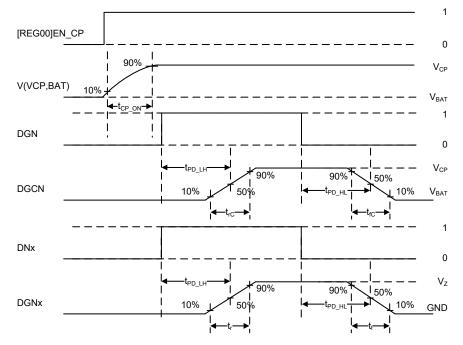

| HS Gate               | Charge Pump                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |                      |                     |      |

| VCP_UVLO+             | V(VCP, BAT) Turn On Level                                           | V(VCP,BAT) rises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                   | 3                    | _                   | V    |

| V <sub>CP_UVLO-</sub> | V(VCP, BAT) Turn Off Level                                          | V(VCP,BAT) falls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                   | 2.5                  | —                   | V    |

| V <sub>CP</sub>       | VCP Output Voltage                                                  | EN_CP='1', BAT=VIN>13V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>IN</sub> +10 | V <sub>IN</sub> +12  | V <sub>IN</sub> +16 | V    |

| t <sub>CP_ON</sub>    | Rising Time of the Voltage<br>Difference between VCP and VBAT       | External capacitor 22nF between<br>VCP and BAT.<br>VIN=36V, V(VCP, BAT) rises from<br>10% to 90% (V <sub>CP</sub> -V <sub>BAT</sub> ) <sup>(Note)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     | 25                   | _                   | ms   |

| f <sub>CP</sub>       | Charge Pump Switching Frequency                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                   | 600                  | _                   | kHz  |

| Gate Driv             |                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                   | 1                    |                     |      |

|                       |                                                                     | DNx='1', V <sub>IN</sub> >13V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                  | 12                   | 16                  | V    |

| Vz                    | DGNx Clamp Voltage                                                  | DNx='1', V <sub>IN</sub> ≤13V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     | V <sub>IN</sub> -0.7 | _                   | V    |

| tr                    | DGNx Rising Time                                                    | C <sub>DGNx</sub> =15nF <sup>(Note)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     | 0.5                  | 1.0                 | μs   |

| t <sub>f</sub>        | DGNx Falling Time                                                   | C <sub>DGNx</sub> =15nF <sup>(Note)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                   | 0.5                  | 1.0                 | μs   |

| t <sub>PD_HL</sub>    | DGNx Falling Propagation Delay<br>Time                              | C <sub>DGNx</sub> =15nF <sup>(Note)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                   | 0.5                  | 1.0                 | μs   |

| t <sub>PD_LH</sub>    | DGNx Rising Propagation Delay<br>Time                               | C <sub>DGNx</sub> =15nF <sup>(Note)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                   | 0.5                  | 1.0                 | μs   |

| t <sub>мм</sub>       | DGNx Delay Time Mismatch                                            | C <sub>DGNx</sub> =15nF. t <sub>MM</sub> =  t <sub>PD_LHx</sub> - t <sub>PD_HLx</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                   | 0.5                  | 1.0                 | μs   |

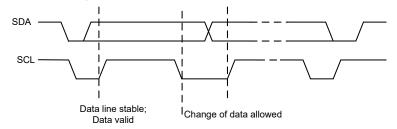

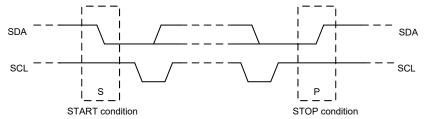

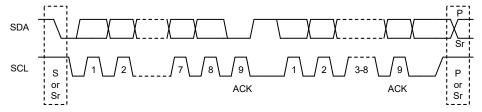

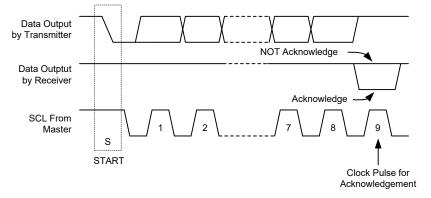

| ISOURCE               | DGNx Source Current                                                 | C <sub>DGNx</sub> =1µF, peak current at DNx<br>'0'→'1' rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                   | 850                  | _                   | mA   |