#### **Features**

- V<sub>IN</sub> Input Range from 7.5V to 36V

- Accumulative Cell Voltage Monitor: 8-to-1 Analog Multiplexer with divided ratio accuracy: 1/n ± 0.5%

- Reverse-current prevention switching scan frequency of 100Hz

- Requires fewer MCU A/D Converters (ADCs)

- 5V/30mA internal Voltage Regulator with ±1% accuracy

- Operating Temperature Range: -40°C to +85°C

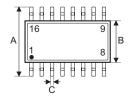

- Package Type: 16-pin NSOP

### **Applications**

- · Electric power tools

- · Handheld vacuum cleaners

### **General Description**

The HT7Q1520 is a high voltage analog-front-end IC for 3 to 8 cell Li-ion rechargeable battery protection. It consists of an accumulative cell voltage monitor and a high accuracy voltage regulator. The device is designed to monitor an accumulative voltage from 1 to N and outputs the divide-by-N voltage to the analog multiplexer with a  $\pm 0.5\%$  divided ratio accuracy. The anti-reverse current switch is implemented to prevent a backflow current even if V<sub>OUT</sub> is higher than V<sub>BATn</sub>. Each divided accumulative cell voltage can be observed sequentially on pin VBATn which will benefit MCUs with a lower number of ADCs. There are 3 control bits, B0, B1 and B2, to select which terminal voltage outputs with a maximum 100Hz scanning frequency when C<sub>OUT</sub>=2.2nF. The enable pin, EN S, is used to close all switches and the output voltage is pulled down by an internal  $1M\Omega$  resistor. An integrated regulator provides a 5V supply to the MCU with a 30mA driving current capability and which has  $\pm 1\%$  precision. The voltage regulator is always active even if the EN S pin is cleared to a logic low level.

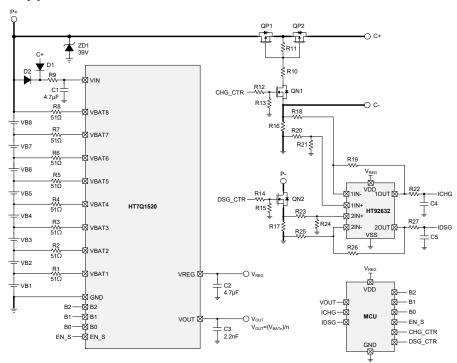

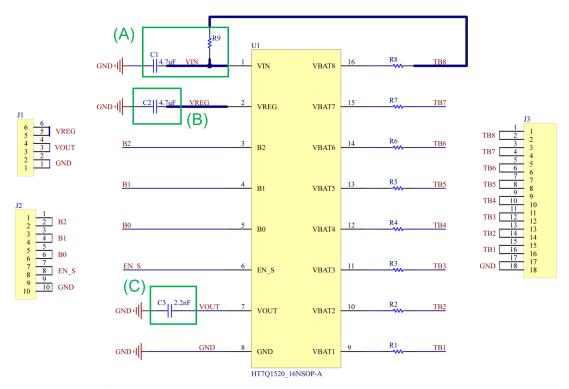

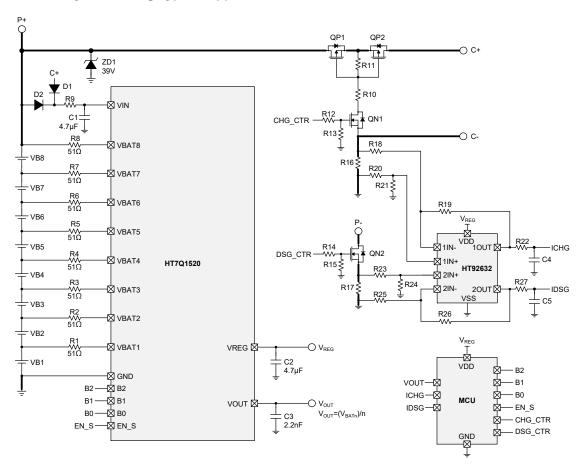

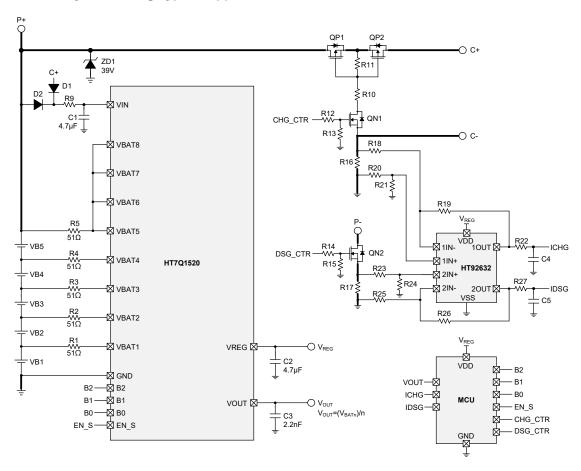

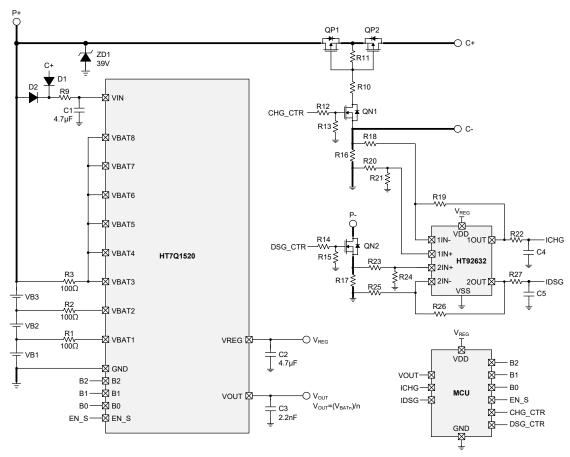

## **Typical Application Circuit**

Note: 1. If less than 8 serial batteries are used, connect the unused VBATn to the highest voltage potential. Do not leave any VBATn pin floating to prevent damage to the device.

- 2. The bold lines indicate that these connections need to be as short as possible.

- 3. VIN pin should not be floating to prevent abnormal operations.

Rev. 1.40 1 November 19, 2021

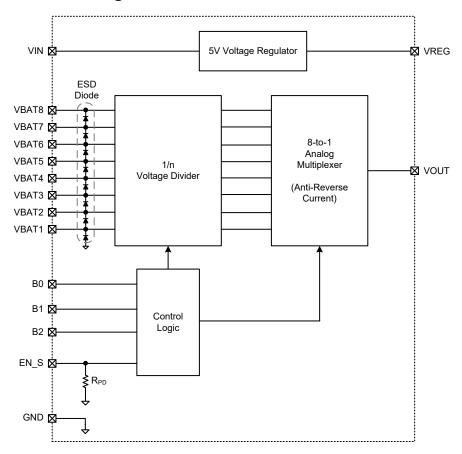

# **Functional Block Diagram**

# **Pin Assignment**

# **Pin Description**

| Pin No. | Pin Name | Туре | Pin Discpription                                                                                      |

|---------|----------|------|-------------------------------------------------------------------------------------------------------|

| 1       | VIN      | Р    | Input supply voltage. Connect to the top VBATn                                                        |

| 2       | VREG     | 0    | Regulator 5V/30mA output. Connect a 4.7µF capacitor to GND                                            |

| 3       | B2       | ı    | 8-to-1 analog multiplexer selection bit - MSB                                                         |

| 4       | B1       | 1    | 8-to-1 analog multiplexer selection bit                                                               |

| 5       | В0       | ı    | 8-to-1 analog multiplexer selection bit - LSB                                                         |

| 6       | EN_S     | ı    | Enable terminal for the 8-to-1 analog multiplexer. Connected to $1M\Omega$ internal pull low resistor |

| 7       | VOUT     | 0    | 8-to-1 analog multiplexer output. Connect a 2.2nF capacitor to GND.                                   |

| 8       | GND      | G    | Ground terminal                                                                                       |

| 9       | VBAT1    | ı    | Battery cell 1 positive terminal and battery cell 2 negative terminal                                 |

| 10      | VBAT2    | ı    | Battery cell 2 positive terminal and battery cell 3 negative terminal                                 |

| 11      | VBAT3    | ı    | Battery cell 3 positive terminal and battery cell 4 negative terminal                                 |

| 12      | VBAT4    | ı    | Battery cell 4 positive terminal and battery cell 5 negative terminal                                 |

| 13      | VBAT5    | ı    | Battery cell 5 positive terminal and battery cell 6 negative terminal                                 |

| 14      | VBAT6    | ı    | Battery cell 6 positive terminal and battery cell 7 negative terminal                                 |

| 15      | VBAT7    | I    | Battery cell 7 positive terminal and battery cell 8 negative terminal                                 |

| 16      | VBAT8    | Ī    | Battery cell 8 positive terminal                                                                      |

# **Absolute Maximum Ratings**

| Parameter                                                                 | Value            | Unit         |      |

|---------------------------------------------------------------------------|------------------|--------------|------|

| V <sub>IN</sub>                                                           | -0.3 to +40      | V            |      |

| V <sub>REG</sub> , V <sub>OUT</sub> , B2, B1, B0, EN_S, V <sub>BAT1</sub> |                  | -0.3 to +5.5 | V    |

| Δ[V <sub>BATi</sub> ~V <sub>BAT(i-1)</sub> ], i=8, 7, 6, 5, 4, 3, 2       |                  | -0.3 to +5.5 | V    |

| Operating Temperature Range                                               | -40 to +85       | °C           |      |

| Maximum Junction Temperature                                              | +125             | °C           |      |

| Storage Temperature Range                                                 |                  | -65 to +160  | °C   |

| Lead Temperature (Soldering 10sec)                                        |                  | +260         | °C   |

| CCD Cussontikility                                                        | Human Body Model | ±6000        | V    |

| ESD Susceptibility                                                        | Machine Model    | ±350         | V    |

| Junction-to-Ambient Thermal Resistance, θ <sub>JA</sub>                   | 16NSOP (150mil)  | 100          | °C/W |

# **Recommended Operating Ratings**

| Parameter       | Value       | Unit |

|-----------------|-------------|------|

| V <sub>IN</sub> | 7.5 to 36.0 | V    |

| Та              | -40 to +85  | °C   |

Note that Absolute Maximum Ratings indicate limitations beyond which damage to the device may occur. Recommended Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specified performance limits.

Rev. 1.40 3 November 19, 2021

## **Electrical Characteristics**

$V_{\text{IN}}\text{=}36\text{V},\,C_{\text{REG}}\text{=}4.7\mu\text{F},\,C_{\text{OUT}}\text{=}2.2n\text{F}$  and Ta=25  $^{\circ}\text{C},\,\text{unless}$  otherwise specified.

| Or made at                                      | Domestratora                                                  | Took Occupitation                                                                         | BA:   | T     | Maria | 11c-14 |

|-------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| Symbol                                          | Parameter                                                     | Test Condition                                                                            | Min.  | Тур.  | Max.  | Unit   |

| Supply and Input                                |                                                               |                                                                                           | Τ_    | I     |       |        |

| V <sub>IN</sub>                                 | Supply Voltage                                                |                                                                                           | 7.5   | _     | 36.0  | V      |

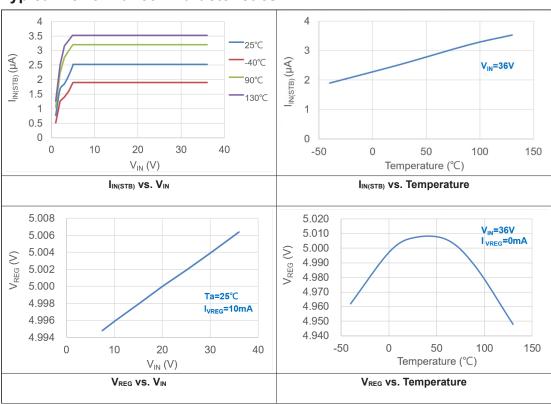

| I <sub>IN(SCAN)</sub>                           | Supply Current – Scan                                         | EN_S=1, Scan B2~B0 with frequency 100Hz                                                   | _     | 2.5   | 4.0   | μΑ     |

| I <sub>IN(STB)</sub>                            | Supply Current – Standby                                      | B0=B1=B2=EN_S=0                                                                           | _     | 2.5   | 4.0   | μΑ     |

| V <sub>Bi</sub>                                 | Cell Voltage Range                                            | i=1~8                                                                                     | 2.5   | _     | 4.5   | V      |

| $I_{Bi}$                                        | Cell Input Leakage Current                                    | V <sub>BATI</sub> =5V×i, EN_S=0,<br>V <sub>IN</sub> =V <sub>BAT8</sub> , i=1~8            | -0.1  | _     | 0.1   | μΑ     |

| I <sub>Bi(ACT)</sub>                            | Cell Input Current when Monitoring Voltage                    | V <sub>BATi</sub> =4.2V×i, EN_S=1,<br>V <sub>IN</sub> =36V, i=1~8                         | 19    | 24    | 35    | μA     |

| I <sub>B1(REV)</sub>                            | VBAT1 Input Reverse Current                                   | V <sub>BAT8</sub> =36V, V <sub>BAT1</sub> =2.5V,<br>B2~B0=0b'111, Measure I <sub>B1</sub> | -0.1  | _     | 0.1   | μA     |

| Voltage Regulator                               | r                                                             |                                                                                           | •     |       |       |        |

| V <sub>REG</sub>                                | Regulator Output Voltage                                      | I <sub>LOAD</sub> =10mA                                                                   | 4.95  | 5.00  | 5.05  | V      |

| I <sub>REG</sub>                                | Regulator Output Current                                      | V <sub>IN</sub> =7.5V, Ta=-40~85°C                                                        | 30    | _     | _     | mA     |

| $\Delta V_{REG}$                                | Load Regulation                                               | I <sub>LOAD</sub> =0~30mA                                                                 | _     | 50    | _     | mV     |

| $\Delta V_{REG}/(V_{REG} \times \Delta V_{IN})$ | Line Regulation                                               | V <sub>IN</sub> =7.5V~36V, I <sub>LOAD</sub> =10mA                                        | _     | 0.02  | _     | %/V    |

| $\Delta V_{REG}/(V_{REG} \times \Delta Ta)$     | Temperature Coefficient                                       | I <sub>LOAD</sub> =1mA, Ta=-40~85°C                                                       | _     | ±100  | _     | ppm/°C |

| Accumulative Cel                                | I Voltage Monitor                                             |                                                                                           |       |       |       |        |

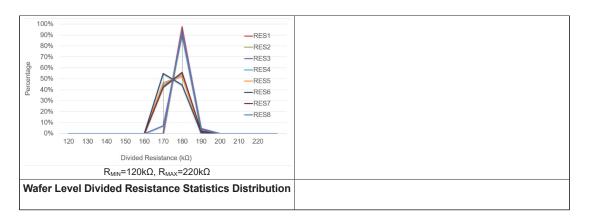

| R                                               | Divided Resistance                                            | _                                                                                         | 120   | 170   | 220   | kΩ     |

|                                                 | VDATO A                                                       | V <sub>BAT8</sub> =20V~36V,<br>B2~B0=0b'111, EN_S=1                                       | 0.995 | 1.000 | 1.005 | _      |

| Ratio8 <sub>(NORM)</sub>                        | VBAT8 Accumulative Cell Voltage<br>Divided Ratio (Normalised) | V <sub>BAT8</sub> =20V~36V,<br>B2~B0=0b'111, EN_S=1,<br>Ta=-40~85°C                       | 0.990 | 1.000 | 1.010 | _      |

|                                                 | VDATZ A savinavilativa Call Valta va                          | V <sub>BAT7</sub> =17.5V~31.5V,<br>B2~B0=0b'110, EN_S=1                                   | 0.995 | 1.000 | 1.005 | _      |

| Ratio7 <sub>(NORM)</sub>                        | VBAT7 Accumulative Cell Voltage<br>Divided Ratio (Normalised) | V <sub>BAT7</sub> =17.5V~31.5V,<br>B2~B0=0b'110, EN_S=1,<br>Ta=-40~85°C                   | 0.990 | 1.000 | 1.010 | _      |

|                                                 | VDATO A comment the Coll Veltage                              | V <sub>BAT6</sub> =15V~27V,<br>B2~B0=0b'101, EN_S=1                                       | 0.995 | 1.000 | 1.005 | _      |

| Ratio6 <sub>(NORM)</sub>                        | VBAT6 Accumulative Cell Voltage<br>Divided Ratio (Normalised) | V <sub>BAT6</sub> =15V~27V,<br>B2~B0=0b'101, EN_S=1,<br>Ta=-40~85°C                       | 0.990 | 1.000 | 1.010 | _      |

|                                                 | VBAT5 Accumulative Cell Voltage                               | V <sub>BAT5</sub> =12.5V~22.5V,<br>B2~B0=0b'100, EN_S=1                                   | 0.995 | 1.000 | 1.005 | _      |

| Ratio5 <sub>(NORM)</sub>                        | Divided Ratio (Normalised)                                    | V <sub>BAT5</sub> =12.5V~22.5V,<br>B2~B0=0b'100, EN_S=1,<br>Ta=-40~85°C                   | 0.990 | 1.000 | 1.010 | _      |

| Ratio4 <sub>(NORM)</sub>                        | VDATA A                                                       | V <sub>BAT4</sub> =10V~18V,<br>B2~B0=0b'011, EN_S=1                                       | 0.995 | 1.000 | 1.005 | _      |

|                                                 | VBAT4 Accumulative Cell Voltage<br>Divided Ratio (Normalised) | V <sub>BAT4</sub> =10V~18V,<br>B2~B0=0b'011, EN_S=1,<br>Ta=-40~85°C                       | 0.990 | 1.000 | 1.010 | _      |

|                                                 | VDATO A communication College                                 | V <sub>BAT3</sub> =7.5V~13.5V,<br>B2~B0=0b'010, EN_S=1                                    | 0.995 | 1.000 | 1.005 | _      |

| Ratio3 <sub>(NORM)</sub>                        | VBAT3 Accumulative Cell Voltage<br>Divided Ratio (Normalised) | V <sub>BAT3</sub> =7.5V~13.5V,<br>B2~B0=0b'010, EN_S=1,<br>Ta=-40~85°C                    | 0.990 | 1.000 | 1.010 | _      |

Rev. 1.40 4 November 19, 2021

| Symbol                   | Parameter                                                     | Test Condition                                                        | Min.  | Тур.  | Max.  | Unit |

|--------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|------|

| Datio                    | VBAT2 Accumulative Cell Voltage                               | V <sub>BAT2</sub> =5V~9V, B2~B0=0b'001,<br>EN_S=1                     | 0.995 | 1.000 | 1.005 | _    |

| Ratio2 <sub>(NORM)</sub> | Divided Ratio (Normalised)                                    | V <sub>BAT2</sub> =5V~9V, B2~B0=0b'001,<br>EN_S=1, Ta=-40~85°C        | 0.990 | 1.000 | 1.010 | _    |

| VDATA A LIC O HAVE       |                                                               | V <sub>BAT1</sub> =2.5V~4.5V,<br>B2~B0=0b'000, EN_S=1                 | 0.995 | 1.000 | 1.005 | _    |

| Ratio1 <sub>(NORM)</sub> | VBAT1 Accumulative Cell Voltage<br>Divided Ratio (Normalised) | V <sub>BAT1</sub> =2.5V~4.5V,<br>B2~B0=0b'000, EN_S=1,<br>Ta=-40~85°C | 0.990 | 1.000 | 1.010 | _    |

| Input Logic              |                                                               |                                                                       |       |       |       |      |

| f <sub>MAX</sub>         | B2~B0 Maximum Scan Frequency                                  | C <sub>OUT</sub> = 2.2nF                                              | 100   | _     | _     | Hz   |

| VIH                      | Input Logic High Threshold                                    | V <sub>IN</sub> =7.5~36V, B2, B1, B0 and EN_S pins                    | 2.5   | _     | _     | V    |

| VIL                      | Input Logic Low Threshold                                     | V <sub>IN</sub> =7.5~36V, B2, B1, B0 and EN_S pins                    | _     | _     | 0.8   | V    |

| R <sub>PD</sub>          | Pull Low Resistance                                           | EN_S pin                                                              | _     | 1     | _     | МΩ   |

| ILEAK                    | Input Logic Leakage                                           | V <sub>IN</sub> =7.5V~36V, B2, B1 and B0 pins                         | _     | _     | 0.1   | μΑ   |

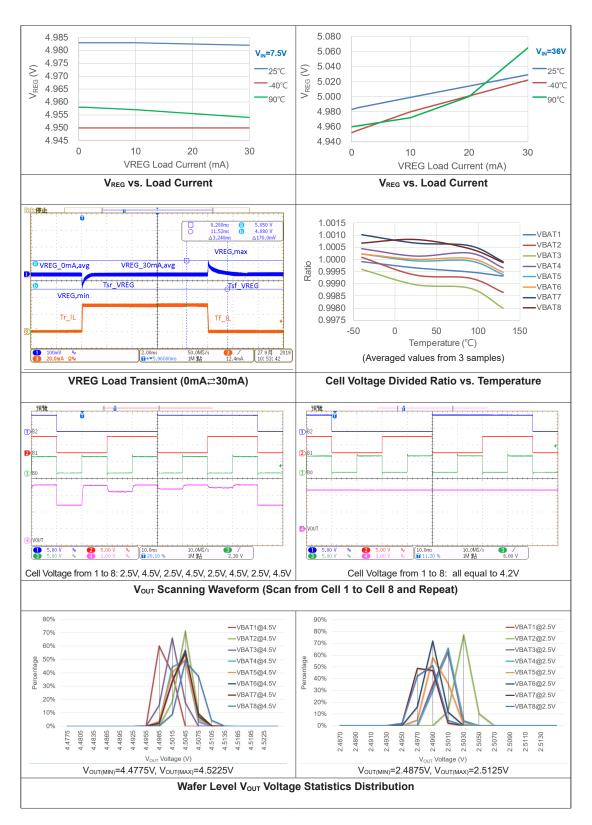

# **Typical Performance Characteristics**

Rev. 1.40 5 November 19, 2021

# **Functional Description**

### **Accumulative Cell Voltage Monitor**

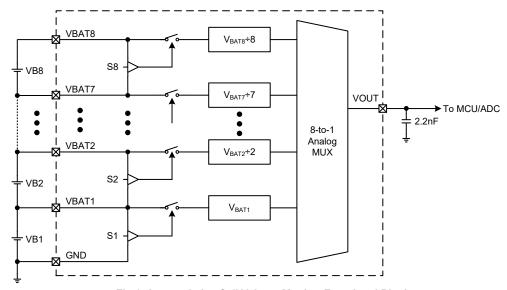

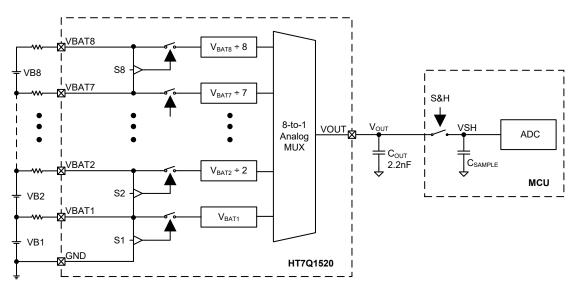

The accumulative cell voltage monitor consists of high voltage switches, voltage dividers and an 8-to-1 analog multiplexer as shown in Fig 1. The high voltage switches are implemented using an anti-reverse current topology which provides isolation between the output voltage and the unselected VBATs.

B2, B1 and B0 are used to control the p-type switches S1~S8 only if EN\_S='H'. The control truth table is shown below. This produces an accumulative cell voltage,  $V_{BATn}$ , divided by "n" on  $V_{OUT}$ . This accurate  $\pm 0.5\%$  voltage divided ratio is designed to minimise any mismatch errors.

| EN_S | B2      | B1       | В0 | S8 | S7 | S6 | S5 | S4 | S3 | S2 | S1 | V <sub>OUT</sub> (V)   |

|------|---------|----------|----|----|----|----|----|----|----|----|----|------------------------|

| 0    | Х       | X        | Х  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                      |

| 1    | 0       | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | V <sub>BAT1</sub> ×1/1 |

| 1    | 0       | 0        | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | V <sub>BAT2</sub> ×1/2 |

| 1    | 0       | 1        | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | V <sub>BAT3</sub> ×1/3 |

| 1    | 0       | 1        | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | V <sub>BAT4</sub> ×1/4 |

| 1    | 1       | 0        | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | V <sub>BAT5</sub> ×1/5 |

| 1    | 1       | 0        | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | V <sub>BAT6</sub> ×1/6 |

| 1    | 1       | 1        | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>BAT7</sub> ×1/7 |

| 1    | 1       | 1        | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>BAT8</sub> ×1/8 |

|      | Power o | n states |    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                      |

**Table 1: Accumulative Cell Voltage Monitor Truth Table**

Rev. 1.40 7 November 19, 2021

Fig 1. Accumulative Cell Voltage Monitor Functional Block

### **Application Information**

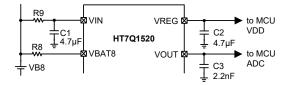

### VIN, VREG, VOUT Capacitors

The VIN input capacitor  $C_{\rm IN}$  and VREG output capacitor  $C_{\rm REG}$  are recommended to have a value of 4.7 $\mu$ F respectively and for better input noise filtering and output load transient behavior. A recommended 2.2 $\mu$ F noise filtering capacitor should be connected between VOUT and GND terminals. Note that higher noise capacitance value of  $C_{\rm OUT}$  will lower the acceptable scan frequency.

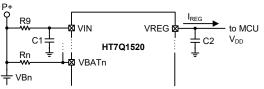

# VIN and VBATn Spike Suppression Resistors

The appropriate VIN and VBATn spike suppression resistors corresponded to R9 and Rn, lower the voltage spike and inrush current applied on any I/O pins, which can improve the stability of V<sub>REG</sub> that provides the power source to the external MCUs. Especially when there are spike filter capacitors connected from P+ or C+ to GND, the VBATn spike suppression resistors(Rn) are necessary. The recommended resistance values of VIN and VBATn resistors depend on the number of battery cells and are listed in Table 2.

| Battery Cells | VIN<br>Recommended<br>Resistor (R9) | VBATn<br>Recommended<br>Resistor (Rn) |

|---------------|-------------------------------------|---------------------------------------|

| 3S            | 18Ω                                 | 100Ω                                  |

| 4S            | 100Ω                                | 51Ω                                   |

| 5S            | 180Ω                                | 51Ω                                   |

| 6S            | 270Ω                                | 51Ω                                   |

| 7S            | 360Ω                                | 51Ω                                   |

| 8S            | 430Ω                                | 51Ω                                   |

Table 2: Spike Suppression Recommended Resistor

It is necessary to select an appropriate package for VIN spike suppression resistor (R9) in order to prevent it being damaged from overheated. The maximum power on R9 can be easily calculated by the following formula:

$$P_{R9.MAX} = (I_{REG})^2 \times R9$$

Where, the  $I_{REG}$  is the maximum VREG output current. The R9 is the resistance value of VIN spike suppression resistor.

It is recommended to select the resistor package that its maximum rated power is greater than twice the  $P_{\text{R9.MAX}}$ .

Rev. 1.40 8 November 19, 2021

#### **Cell Voltage Monitor Scan Frequency**

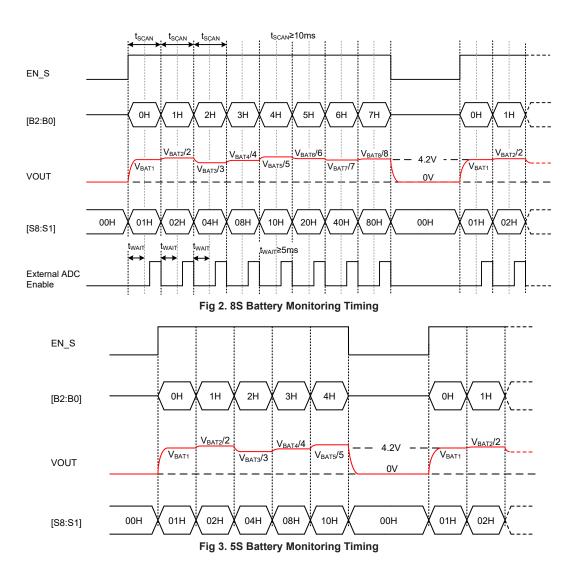

The HT7Q1520 device can output accumulative cell voltage to external MCU/ADC for monitoring battery voltage status. The Fig2 and Fig3 show the timing diagrams of cell voltage monitor scanning for 5S and 8S applications. The HT7Q1520 starts to charge the VOUT capacitor from 0V to the selected cell voltage when the EN S receives an 'L' to 'H' signal. In order to insure

the external MCU A/D conversion accuracy, the A/D conversion procedure has to wait before the HT7Q1520's VOUT capacitor is fully charged. The suggested minimum waiting time is 5ms after EN\_S rises from 'L' to 'H' or cell voltage monitor channel is switched. It is recommended that the maximum scan frequency for accumulative cell voltage monitoring is less than 100Hz and that EN\_S='0' when the voltage scanning procedure has finished for power saving purposes.

Rev. 1.40 9 November 19, 2021

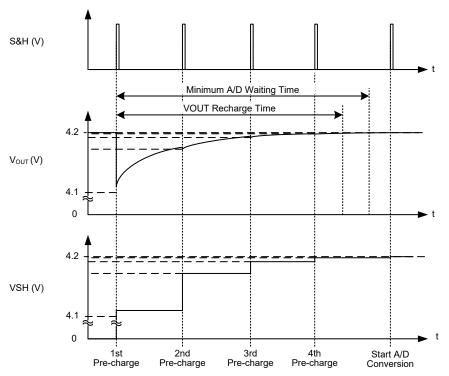

# Acquiring Cell Voltage Monitor Output with External MCU ADC

The HT7Q1520 could output the battery cell voltage to an external MCU for monitoring the battery status when it is in charging or discharging state. As shown in Fig.4, the external MCU ADC samples the  $V_{\text{OUT}}$  voltage via an ADC sampling capacitor ( $C_{\text{SAMPLE}}$ ), which is typically 5pF to 50pF. Due to the charge sharing effect, the voltage on the VOUT capacitor

( $C_{OUT}$ ) drops while the ADC samples that with the initially zero-voltage  $C_{SAMPLE}$ . A voltage-drop occurs on the  $C_{OUT}$  after the first ADC sampling, and then it needs a recharge time to recharge the  $C_{OUT}$ . Referring to Fig.5, a pre-charge procedure of  $C_{SAMPLE}$  during the VOUT capacitor recharge time is recommended to minimize the charge sharing effect by means of performing several sampling without clearing the charges in the  $C_{SAMPLE}$ .

Fig 4. HT7Q1520 + MCU/ADC Functional Block

Fig 5. ADC Sampling Recommended Timing

Rev. 1.40 10 November 19, 2021

For the best conversion accuracy, the A/D conversion has to wait before the C<sub>OUT</sub> recharge is complete. The recommended minimum waiting time from the first sampling to A/D conversion beginning is listed in Table 3.

| MCU/ADC Sampling Capacitance (pF)         | 5   | 10  | 20  | 30   | 40   | 50   |

|-------------------------------------------|-----|-----|-----|------|------|------|

| Recommended minimum A/D waiting time (μs) | 370 | 660 | 950 | 1120 | 1240 | 1340 |

**Table 3. ADC Recommended Waiting Time**

### **Voltage Spike Suppression Method**

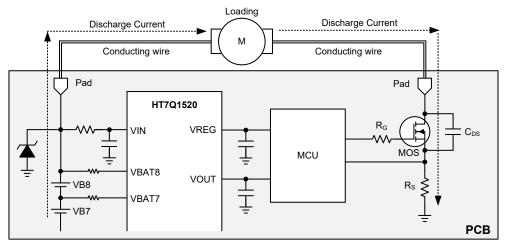

Fig 6. Simplified Typical BMS System Discharge Path Diagram

Most battery-management systems would monitor charge and discharge current to prevent over-current damage. Due to the parasitic inductance on conducting wires and PCB layout connections, a large voltage spike may occur while the MCU-controlled MOS rapidly shuts down the charge or discharge current, and this spike may damage HT7Q1520 VBATn or VIN pins. Any voltage spike on the VBATn and VIN pins should not over the limitation in Absolute Maximum Ratings, which is 40V. Four recommended measures listed below would help to reduce the voltage spike.

- Ensure that the external conducting wires and PCB layout connections where large charge or discharge current flows are as short as possible.

- 2. Adjust the slew rate of MOS switch with the Gate resistor R<sub>G</sub>. Turn off the MOS switch with a slower slew rate can lower voltage spike, however the trade off is a slower protection response time.

- Add a capacitor (C<sub>DS</sub>) between the drain and source nodes of the MOS switch as shown in Fig6. The recommended capacitance is 0.1μF to 0.22μF.

- Add a 39V Zener diode between the highest voltage potential node of the battery cells and GND.

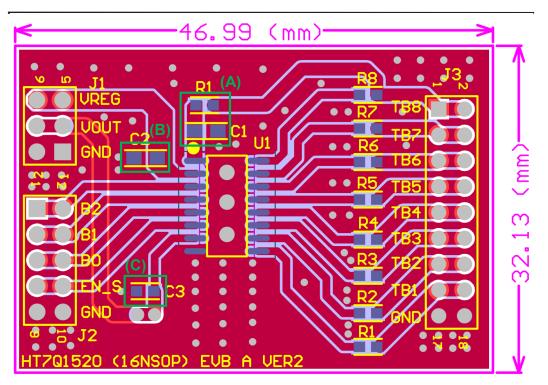

### **PCB Layout Considerations**

The following placement/layout guidelines are suggested for the sake of noise reduction and voltage spike suppression.

- 1. The VIN filter capacitor and resistor must be placed close to the VIN pin. [Region (A)]

- 2. The VREG regulation and noise filter capacitor must be placed close to the VREG pin. [Region (B)]

- 3. The VOUT noise filter capacitor must be placed close to the VOUT pin. [Region (C)]

- 4. Placing a ground line between VIN and VREG lines would improve the ability of resisting surge.

- The tracks where large current would flow through should be wide and short to suppress the voltage spike at the time when MOS switch changes its ON/OFF state.

- The power ground and signal ground should be connected at final output pad (B-) for less noise disturbance.

Rev. 1.40 11 November 19, 2021

### **Evaluation Board**

Fig 7. HT7Q1520 Evaluation Board Schematic

Fig 8. HT7Q1520 Evaluation Board Layout

Rev. 1.40 12 November 19, 2021

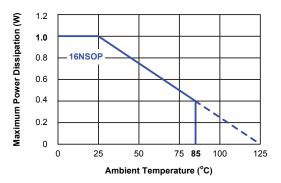

## **Thermal Consideration**

The maximum power dissipation depends upon the thermal resistance of the IC package, PCB layout, rate of surrounding airflow and difference between the junction and ambient temperature. The maximum power dissipation can be calculated using the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - Ta) / \theta_{JA}$$

(W)

where  $T_{J(MAX)}$  is the maximum junction temperature, Ta is the ambient temperature and  $\theta_{JA}$  is the junction-to-ambient thermal resistance of the IC package.

For maximum operating rating conditions, the maximum junction temperature is 125°C. However, it is recommended that the maximum junction temperature does not exceed 125°C during normal operation to maintain high reliability. The de-rating curve of the maximum power dissipation is shown below:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (100^{\circ}C/W) = 1.0W$$

(16NSOP)

For a fixed  $T_{J(MAX)}$  of  $125^{\circ}C$ , the maximum power dissipation depends upon the operating ambient temperature and the package's thermal resistance,  $\theta_{JA}$ . The derating curve below shows the effect of rising ambient temperature on the maximum recommended power dissipation.

Rev. 1.40 13 November 19, 2021

# **Application Circuits**

## **8S Battery Monitoring Typical Application Circuit**

Rev. 1.40 November 19, 2021

### **5S Battery Monitoring Typical Application Circuit**

Rev. 1.40 15 November 19, 2021

### **3S Battery Monitoring Typical Application Circuit**

Note: 1. If less than 8 serial batteries are used, connect the unused VBATn to the highest voltage potential. Do not leave any VBATn floating to prevent damage to the device.

- 2. For the selection of R9, R1, R2 and R3 resistances, refer to the "VIN and VBATn Spike Suppression Resistors" section for more details.

- 3. VIN pin should not be floating to prevent abnormal operations.

Rev. 1.40 16 November 19, 2021

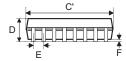

# **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>package information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Further Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- Packing Meterials Information

- Carton information

Rev. 1.40 17 November 19, 2021

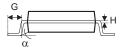

# 16-pin NSOP (150mil) Outline Dimensions

| Symbol |       | Dimensions in inch |       |  |  |  |  |  |

|--------|-------|--------------------|-------|--|--|--|--|--|

| Symbol | Min.  | Nom.               | Max.  |  |  |  |  |  |

| А      | _     | 0.236 BSC          | _     |  |  |  |  |  |

| В      | _     | 0.154 BSC          | _     |  |  |  |  |  |

| С      | 0.012 | _                  | 0.020 |  |  |  |  |  |

| C'     | _     | 0.390 BSC          | _     |  |  |  |  |  |

| D      | _     | _                  | 0.069 |  |  |  |  |  |

| E      | _     | 0.050 BSC          | _     |  |  |  |  |  |

| F      | 0.004 | _                  | 0.010 |  |  |  |  |  |

| G      | 0.016 | _                  | 0.050 |  |  |  |  |  |

| Н      | 0.004 | _                  | 0.010 |  |  |  |  |  |

| α      | 0°    | _                  | 8°    |  |  |  |  |  |

| Symbol | Dimensions in mm |           |      |  |  |  |  |

|--------|------------------|-----------|------|--|--|--|--|

| Symbol | Min.             | Nom.      | Max. |  |  |  |  |

| A      | _                | 6.000 BSC | _    |  |  |  |  |

| В      | _                | 3.900 BSC | _    |  |  |  |  |

| С      | 0.31             | _         | 0.51 |  |  |  |  |

| C'     | _                | 9.900 BSC | _    |  |  |  |  |

| D      | _                | _         | 1.75 |  |  |  |  |

| E      | _                | 1.270 BSC | _    |  |  |  |  |

| F      | 0.10             | _         | 0.25 |  |  |  |  |

| G      | 0.40             | _         | 1.27 |  |  |  |  |

| Н      | 0.10             | _         | 0.25 |  |  |  |  |

| α      | 0°               | _         | 8°   |  |  |  |  |

Rev. 1.40 18 November 19, 2021

### Copyright<sup>©</sup> 2021 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.

Rev. 1.40 19 November 19, 2021