## HT32F67233 Datasheet

32-Bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ Sub-1GHz GFSK RF Transceiver Microcontroller, up to 32 KB Flash and 4 KB SRAM with 1 Msps ADC, USART, UART, SPI, I<sup>2</sup>C, GPTM, SCTM, BFTM, WDT

Revision: V1.10 Date: March 15, 2024

www.holtek.com

## **Table of Contents**

| 1 | General Description                                             | . 6 |

|---|-----------------------------------------------------------------|-----|

| 2 | Features                                                        | . 7 |

|   | Core                                                            | 7   |

|   | On-chip Memory                                                  | 7   |

|   | Flash Memory Controller – FMC                                   | 7   |

|   | Reset Control Unit – RSTCU                                      | 8   |

|   | Clock Control Unit – CKCU                                       | 8   |

|   | Power Management – PWRCU                                        | 8   |

|   | External Interrupt/Event Controller – EXTI                      | 8   |

|   | Analog to Digital Converter – ADC                               | 9   |

|   | I/O Ports – GPIO                                                | 9   |

|   | General-Purpose Timer – GPTM                                    | 9   |

|   | Single Channel Timer – SCTM                                     | 10  |

|   | Basic Function Timer – BFTM                                     | 10  |

|   | Watchdog Timer – WDT                                            | 10  |

|   | Inter-integrated Circuit – I <sup>2</sup> C                     | 10  |

|   | Serial Peripheral Interface – SPI                               | 11  |

|   | Universal Synchronous Asynchronous Receiver Transmitter – USART |     |

|   | Universal Asynchronous Receiver Transmitter – UART              | 12  |

|   | RF Module                                                       | 12  |

|   | Debug Support                                                   | 13  |

|   | Package and Operation Temperature                               | 13  |

| 3 | Overview                                                        | 14  |

|   | Device Information                                              | 14  |

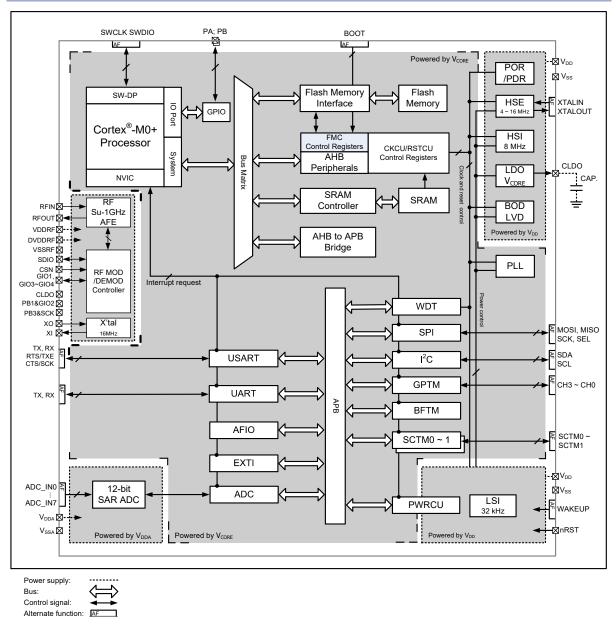

|   | Block Diagram                                                   | 15  |

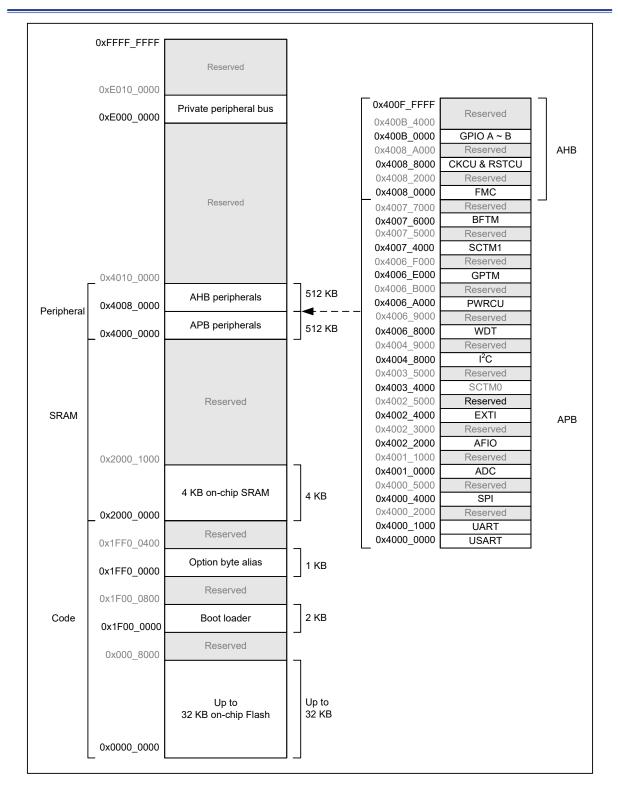

|   | Memory Map                                                      | 16  |

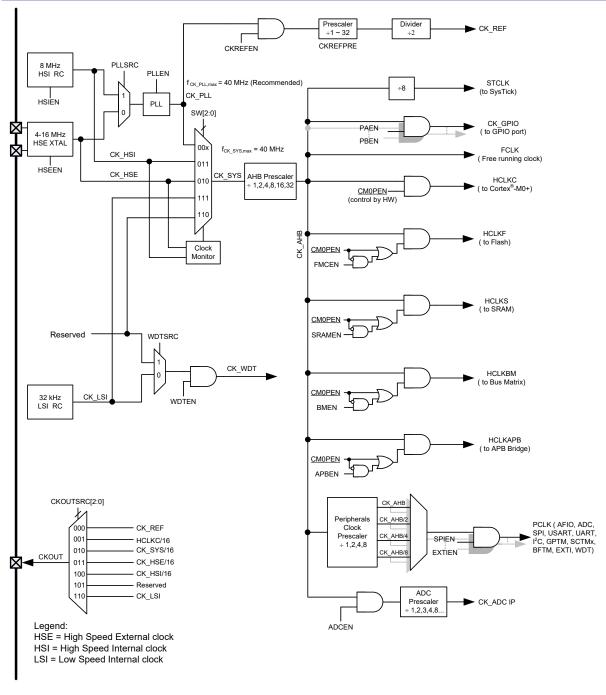

|   | Clock Structure                                                 | 18  |

| 4 | RF Module                                                       | 19  |

| Ċ | Memory Mapping                                                  |     |

|   | SFR Mapping and Bit Definition                                  |     |

|   | Special Function Description                                    |     |

|   | Abbreviation                                                    |     |

|   | Application Circuits                                            |     |

| _ |                                                                 |     |

| 5 | Pin Assignment                                                  | 80  |

| 6 | Electrical Characteristics                                      | . 84 |

|---|-----------------------------------------------------------------|------|

|   | Absolute Maximum Ratings                                        | . 84 |

|   | Recommended DC Operating Conditions                             | . 84 |

|   | RF Characteristics                                              | . 84 |

|   | RF SPI Characteristics                                          | . 87 |

|   | On-Chip LDO Voltage Regulator Characteristics                   | . 87 |

|   | Power Consumption                                               | . 88 |

|   | Reset and Supply Monitor Characteristics                        | . 88 |

|   | External Clock Characteristics                                  | . 89 |

|   | Internal Clock Characteristics                                  | . 90 |

|   | PLL Characteristics                                             | . 90 |

|   | Memory Characteristics                                          | . 90 |

|   | I/O Port Characteristics                                        | . 91 |

|   | ADC Characteristics                                             | . 92 |

|   | SCTM/GPTM Characteristics                                       | . 93 |

|   | I <sup>2</sup> C Characteristics                                | . 93 |

|   | SPI Characteristics                                             | . 94 |

| 7 | Package Information                                             | . 96 |

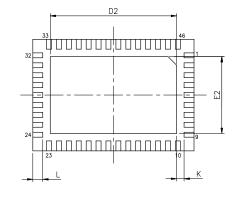

|   | SAW Type 46-pin QFN (6.5mm × 4.5mm × 0.75mm) Outline Dimensions | . 97 |

## **List of Tables**

| Table 1. Features and Peripheral List                     | 14 |

|-----------------------------------------------------------|----|

| Table 2. Register Map                                     | 17 |

| Table 3. SPI Command Format                               | 52 |

| Table 4. Pin Assignment for 46-pin SSOP Package           | 81 |

| Table 5. Pin Description                                  | 82 |

| Table 6. Absolute Maximum Ratings                         | 84 |

| Table 7. Recommended DC Operating Conditions              | 84 |

| Table 8. RF Characteristics                               | 84 |

| Table 9. RF SPI Characteristics                           | 87 |

| Table 10. LDO Characteristics                             | 87 |

| Table 11. Power Consumption Characteristics               | 88 |

| Table 12. V <sub>DD</sub> Power Reset Characteristics     | 88 |

| Table 13. LVD/BOD Characteristics                         | 89 |

| Table 14. High Speed External Clock (HSE) Characteristics | 89 |

| Table 15. High Speed Internal Clock (HSI) Characteristics | 90 |

| Table 16. Low Speed Internal Clock (LSI) Characteristics  |    |

| Table 17. PLL Characteristics                             | 90 |

| Table 18. Flash Memory Characteristics                    | 90 |

| Table 19. I/O Port Characteristics                        | 91 |

| Table 20. ADC Characteristics                             | 92 |

| Table 21. SCTM/GPTM Characteristics                       | 93 |

| Table 22. I <sup>2</sup> C Characteristics                | 93 |

| Table 23. SPI Characteristics                             | 94 |

## **List of Figures**

| Figure 1. Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Figure 2. Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      |

| Figure 3. Clock Structure                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |

| Figure 4. Strobe Command Followed by n-byte Data (CmdD)                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |

| Figure 5. Strobe Command Only (CmdO)                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      |

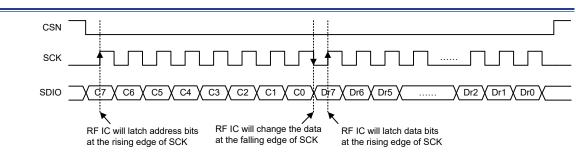

| Figure 6. 3-Wire SPI Interface Write 1-byte Data Operation                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |

| Figure 7. 3-Wire SPI Interface Read 1-byte Data Operation                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |

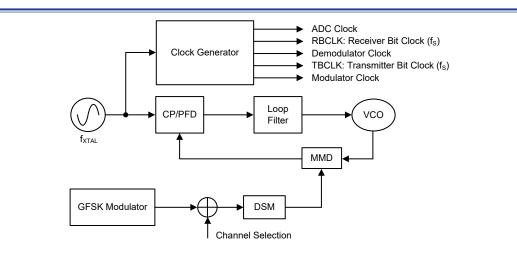

| Figure 8. RF Transceiver System Clock                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

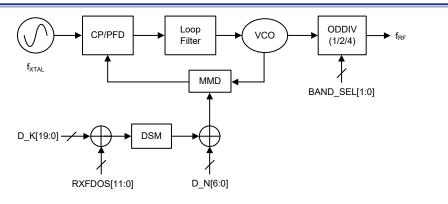

| Figure 9. RF Transceiver Frequency Synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      |

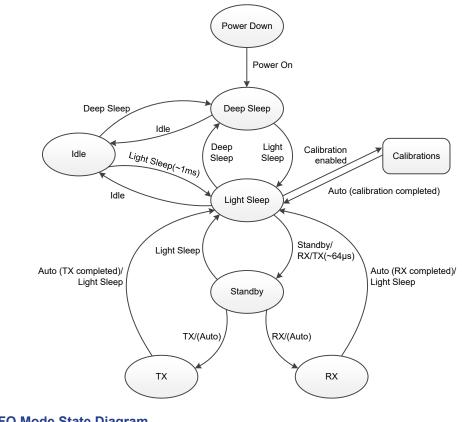

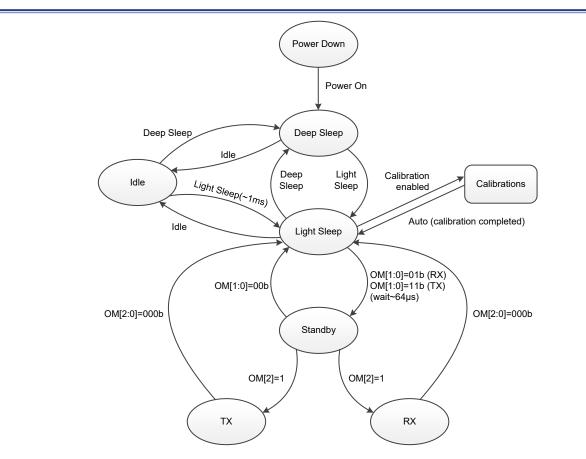

| Figure 10. FIFO Mode State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |

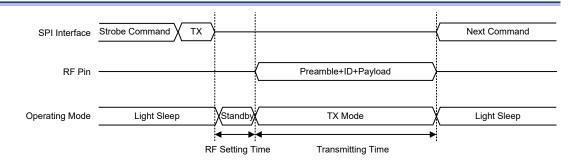

| Figure 11. TX Timing in FIFO Mode                                                                                                                                                                                                                                                                                                                                                                                                                               | . 56                                                 |

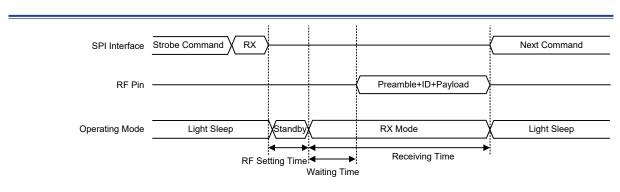

| Figure 12. RX Timing in FIFO Mode                                                                                                                                                                                                                                                                                                                                                                                                                               | . 56                                                 |

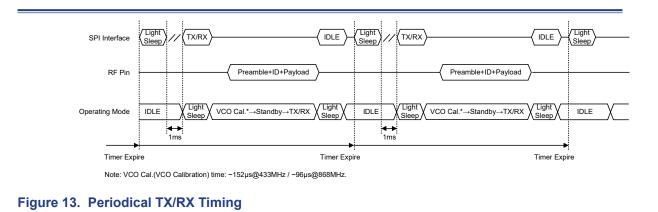

| Figure 13. Periodical TX/RX Timing                                                                                                                                                                                                                                                                                                                                                                                                                              | . 57                                                 |

| Figure 14. Direct Mode State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                            | . 58                                                 |

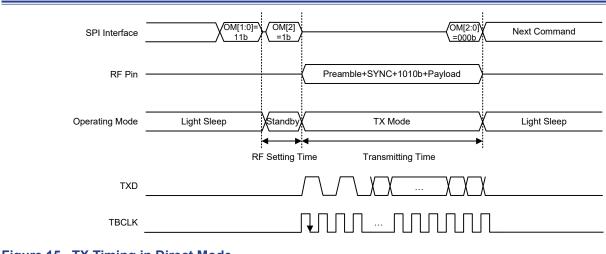

| Figure 15. TX Timing in Direct Mode                                                                                                                                                                                                                                                                                                                                                                                                                             | . 58                                                 |

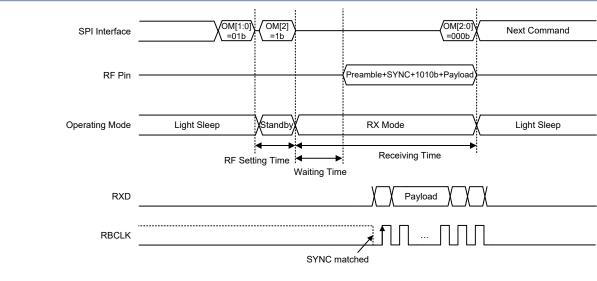

| Figure 16. RX Timing in Direct Mode                                                                                                                                                                                                                                                                                                                                                                                                                             | . 59                                                 |

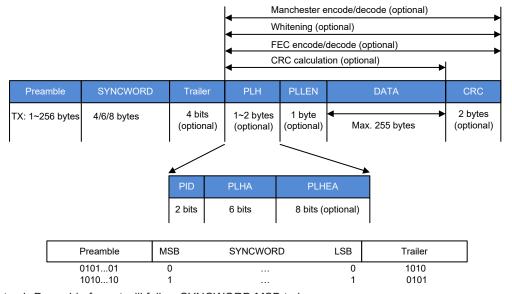

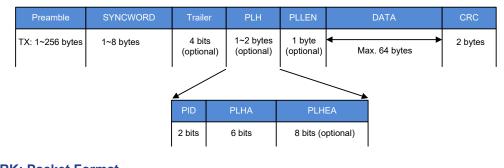

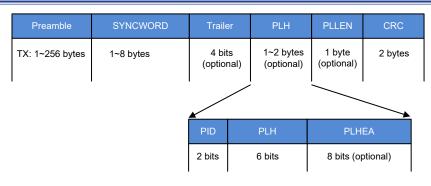

| Figure 17. RF Transceiver Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                         | . 60                                                 |

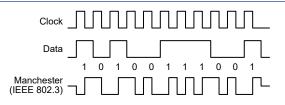

| Figure 18. Manchester Code Example                                                                                                                                                                                                                                                                                                                                                                                                                              | . 62                                                 |

| Figure 19. Simple FIFO Mode Programming Procedure                                                                                                                                                                                                                                                                                                                                                                                                               | . 63                                                 |

| Figure 20. Block FIFO Mode Programming Procedure                                                                                                                                                                                                                                                                                                                                                                                                                | . 64                                                 |

| Figure 21. Extend FIFO Mode Programming Procedure                                                                                                                                                                                                                                                                                                                                                                                                               | . 65                                                 |

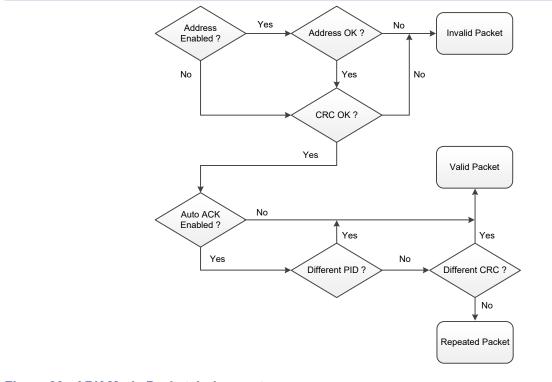

| Figure 22. RX Mode Packet Judgement                                                                                                                                                                                                                                                                                                                                                                                                                             | . 66                                                 |

| Figure 23. ARK Mode Packet Judgement                                                                                                                                                                                                                                                                                                                                                                                                                            | . 66                                                 |

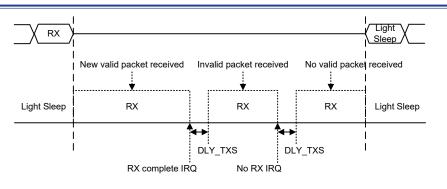

| Figure 24. Continuous RX Mode                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 67                                                 |

| Figure 25. ARK: Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 68                                                 |

| Figure 26. Auto-Resend: Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                           | . 68                                                 |

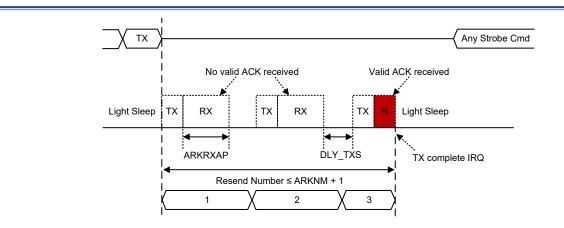

| Figure 27. Auto-resend: ACK Packet Received before ARKNM Limit                                                                                                                                                                                                                                                                                                                                                                                                  | . 69                                                 |

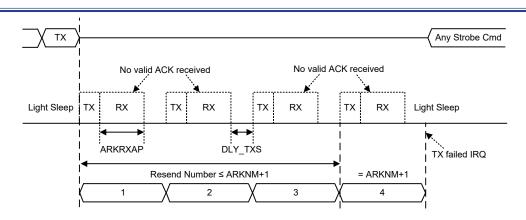

| Figure 28. Auto-resend: No Valid Packet Received before ARKNM Limit                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

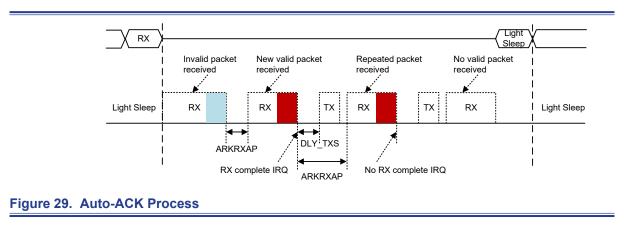

| Figure 29. Auto-ACK Process                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 70                                                 |

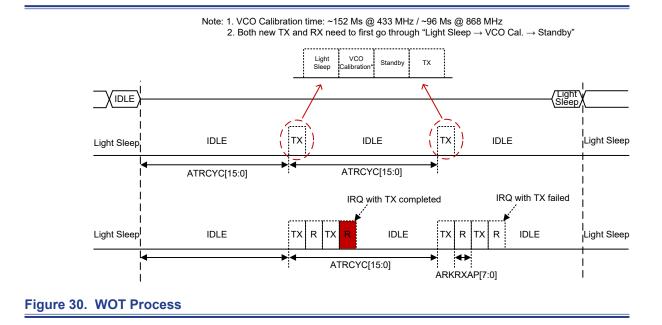

| Figure 30. WOT Process                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 71                                                 |

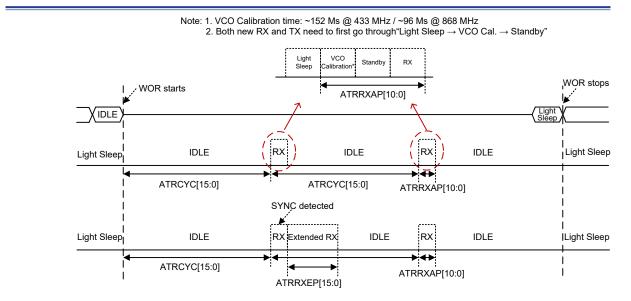

| Figure 31. WOR Without Incoming Packet Received                                                                                                                                                                                                                                                                                                                                                                                                                 | . 72                                                 |

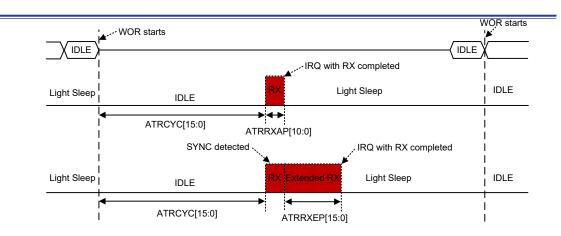

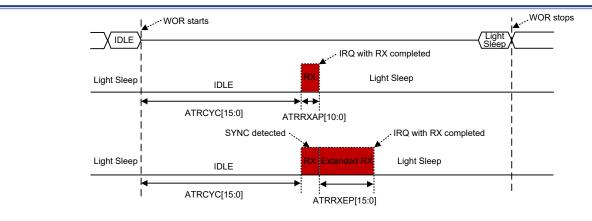

| Figure 32. WOR With Incoming Packet Received                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |

| Figure 33. WOR Stops after Receiving Incoming Packet                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      |

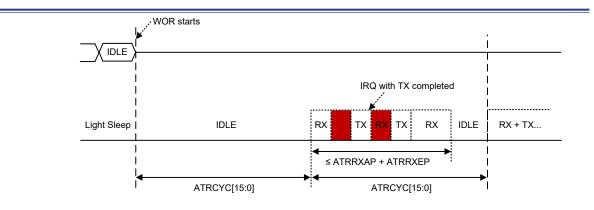

| Figure 34. WOR + ARK Process                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |

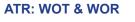

| Figure 35. ATR Message Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

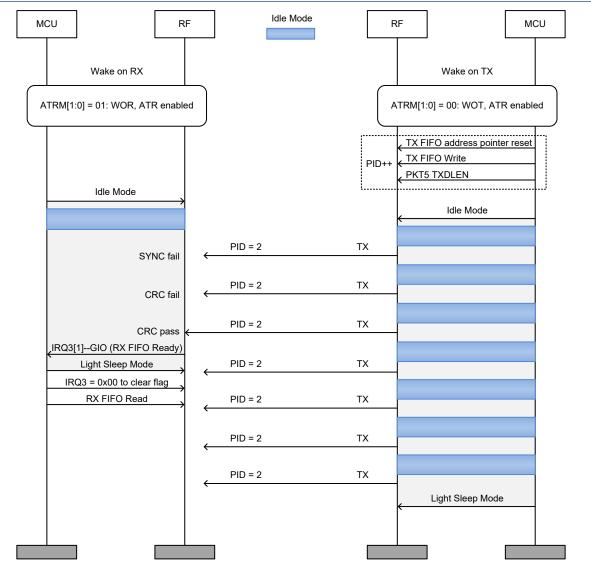

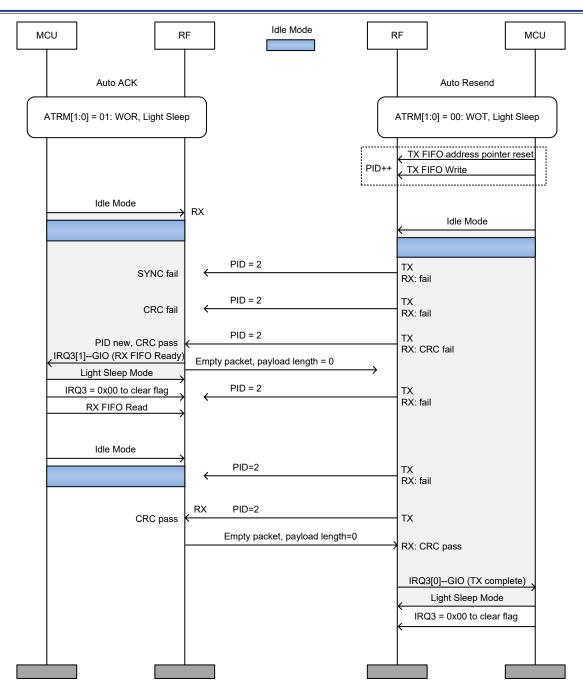

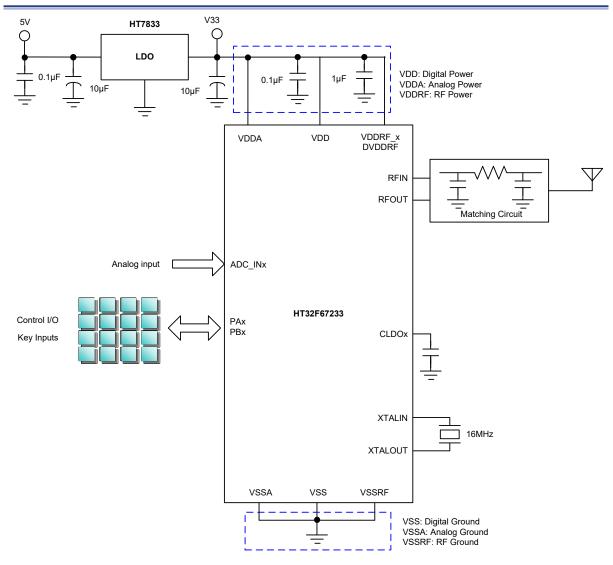

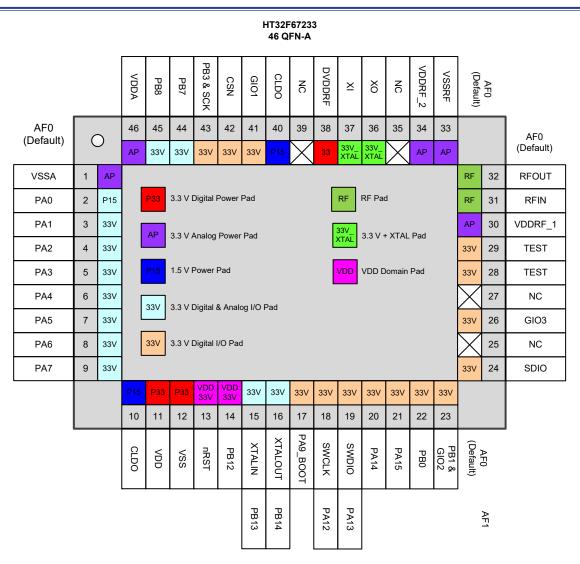

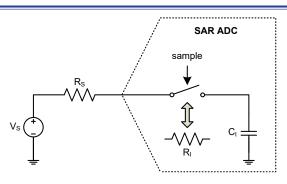

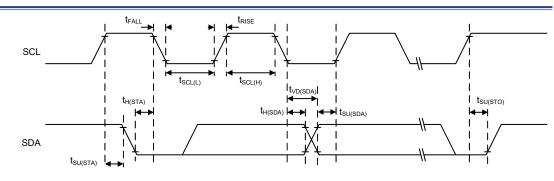

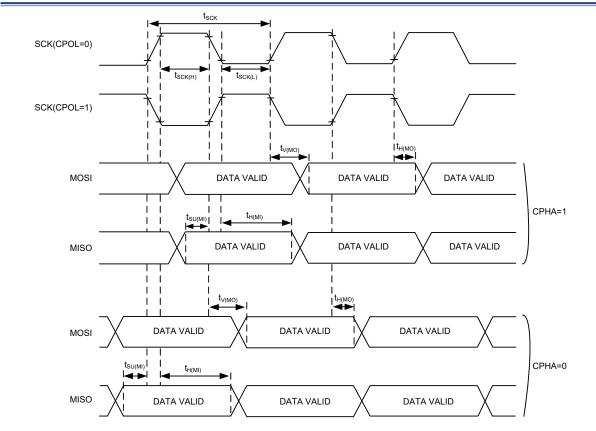

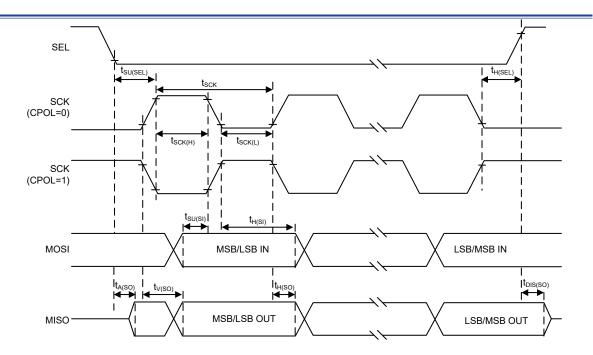

| Figure 36. ATR + ARK Message Flowchart Example 1<br>Figure 36. ATR + ARK Message Flowchart Example 2<br>Figure 37. ATR + ARK Message Flowchart Example 2<br>Figure 38. RF Transceiver Application Circuit.<br>Figure 39. 46-pin QFN Pin Assignment<br>Figure 40. ADC Sampling Network Model<br>Figure 41. I <sup>2</sup> C Timing Diagrams<br>Figure 42. SPI Timing Diagrams – SPI Master Mode<br>Figure 43. SPI Timing Diagrams – SPI Slave Mode with CPHA = 1 | . 75<br>. 76<br>. 79<br>. 80<br>. 92<br>. 94<br>. 95 |

# **1** General Description

The Holtek HT32F67233 is high performance, low power consumption 32-bit microcontrollers based around an Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ processor core. The Cortex<sup>®</sup>-M0+ is a next-generation processor core which is tightly coupled with Nested Vectored Interrupt Controller (NVIC), SysTick timer, and including advanced debug support.

The device operates at a frequency of up to 40 MHz for HT32F67233 with a Flash accelerator to obtain maximum efficiency. It provides up to 32 KB of embedded Flash memory for code/data storage and 4 KB of embedded SRAM memory for system operation and application program usage. A variety of peripherals, such as ADC, I<sup>2</sup>C, USART, UART, SPI, GPTM, SCTM, BFTM, WDT, SW-DP (Serial Wire Debug Port), etc., are also implemented in the device series. Several power saving modes provide the flexibility for maximum optimization between wakeup latency and power consumption, an especially important consideration in low power applications.

The RF module is a high performance and low cost OOK/GFSK transceiver for wireless applications in the 315 MHz, 433 MHz, 470 MHz, 868 MHz and 915 MHz frequency bands. It incorporates a highly integrated sub-1GHz transceiver and a baseband modem with programmable GFSK data rates from 2 Kbps to 250 Kbps and OOK data rates from 0.5 Kbps to 20 Kbps. Data handling features include 64-byte TX/RX FIFO and packet handling such as CRC generation, Forward Error Correction and data whitening, Manchester encoding.

The RF module is optimized for the very low power consumption applications. At 433 MHz band, its RX mode is operated at 5.9 mA and it delivers +19 dBm TX output power at 71 mA current consumption. A low-noise low-IF receiver can achieve -117 dBm sensitivity of 2 Kbps data rate at 433 MHz bands. A Class-E Power Amplifier can deliver up to +20 dBm output power at 433/868 MHz bands. A fully integrated Fractional-N synthesizer can support a wide frequency range with a fine resolution. Both loop filter and XO load capacitors are integrated to on-chip to minimize the requirement for external components.

External MCU can access the RF module through a 3-wire or 4-wire SPI interface. The device supports short strobe commands to reduce the loading of the MCU while maintaining wireless communication link.

Additional link layer features like RSSI for channel assessment, auto-acknowledgement and autoresend, WOT and WOR, etc., facilitate microcontroller based ISM bands wireless link applications.

The above features ensure that the device is suitable for use in a wide range of applications, especially in areas such as industrial control (meter and data logging), smart home appliances (security products, sensor and alarm system), remote control (keyless entry), industrial/agricultural automation, data acquisition and recording and so on.

## arm Cortex

# **2** Features

## Core

- 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ processor core

- Up to 40 MHz operating frequency

- Single-cycle multiplication

- Integrated Nested Vectored Interrupt Controller (NVIC)

- 24-bit SysTick timer

The Cortex<sup>®</sup>-M0+ processor is a very low gate count, highly energy efficient processor that is intended for microcontroller and deeply embedded applications that require an area optimized, low-power processor. The processor is based on the ARMv6-M architecture and supports Thumb<sup>®</sup> instruction sets; single-cycle I/O port; hardware multiplier and low latency interrupt respond time.

## **On-chip Memory**

- Up to 32 KB on-chip Flash memory for instruction/data and options storage

- 4 KB on-chip SRAM

- Supports multiple boot modes

The Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ processor accesses and debug accesses share the single external interface to external AHB peripherals. The processor accesses take priority over debug accesses. The maximum address range of the Cortex<sup>®</sup>-M0+ is 4 GB since it has a 32-bit bus address width. Additionally, a pre-defined memory map is provided by the Cortex<sup>®</sup>-M0+ processor to reduce the software complexity of repeated implementation by different device vendors. However, some regions are used by the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ system peripherals. Refer to the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ Technical Reference Manual for more information. Figure 2 shows the memory map of the device, including code, SRAM, peripheral, and other pre-defined regions.

## Flash Memory Controller – FMC

- Flash accelerator for maximum efficiency

- 32-bit word programming with In System Programming Interface (ISP) and In Application Programming (IAP)

- Flash protection capability to prevent illegal access

The Flash Memory Controller, FMC, provides all the necessary functions and pre-fetch buffer for the embedded on-chip Flash Memory. Since the access speed of the Flash Memory is slower than the CPU, a wide access interface with a pre-fetch buffer and cache are provided for the Flash Memory in order to reduce the CPU waiting time which will cause CPU instruction execution delays. Flash Memory word program/page erase functions are also provided.

## **Reset Control Unit – RSTCU**

- Supply supervisor:

- Power On Reset / Power Down Reset POR/PDR

- Brown-out Detector BOD

- Programmable Low Voltage Detector LVD

The Reset Control Unit, RSTCU, has three kinds of reset, a power on reset, a system reset and an APB unit reset. The power on reset, known as a cold reset, resets the full system during power up. A system reset resets the processor core and peripheral IP components with the exception of the SW-DP controller. The resets can be triggered by an external signal, internal events and the reset generators.

## **Clock Control Unit – CKCU**

- External 4 to 16 MHz crystal oscillator

- Internal 8 MHz RC oscillator trimmed to ±2 % accuracy at 3.3 V operating voltage and 25 °C operating temperature

- Internal 32 kHz RC oscillator

- Integrated system clock PLL

- Independent clock divider and gating bits for peripheral clock sources

The Clock Control unit, CKCU, provides a range of oscillator and clock functions. These include a High Speed Internal RC oscillator (HSI), a High Speed External crystal oscillator (HSE), a Low Speed Internal RC oscillator (LSI), a Phase Lock Loop (PLL), a HSE clock monitor, clock prescalers, clock multiplexers, APB clock divider and gating circuitry. The AHB, APB and Cortex<sup>®</sup>-M0+ clocks are derived from the system clock (CK\_SYS) which can come from the HSI, HSE or PLL. The Watchdog Timer uses the LSI as its clock source.

## **Power Management – PWRCU**

- Single  $V_{DD}$  power supply: 2.0 V to 3.6 V

- Integrated 1.5 V LDO regulator for MCU core, peripherals and memories power supply

- Two power domains: V<sub>DD</sub>, V<sub>CORE</sub>

- Four power saving modes: Sleep, Deep-Sleep1, Deep-Sleep2, Power-Down

Power consumption can be regarded as one of the most important issues for many embedded system applications. Accordingly the Power Control Unit, PWRCU, in the device provides many types of power saving modes such as Sleep, Deep-Sleep1, Deep-Sleep2 and Power-Down mode. These operating modes reduce the power consumption and allow the application to achieve the best trade-off between the conflicting demands of CPU operating time, speed and power consumption.

## External Interrupt/Event Controller – EXTI

- Up to 16 EXTI lines with configurable trigger source and type

- All GPIO pins can be selected as EXTI trigger source

- Source trigger type includes high level, low level, negative edge, positive edge, or both edge

- Individual interrupt enable, wakeup enable and status bits for each EXTI line

- Software interrupt trigger mode for each EXTI line

- Integrated deglitch filter for short pulse blocking

The External Interrupt/Event Controller, EXTI, comprises 16 edge detectors which can generate a wake-up event or interrupt requests independently. Each EXTI line can also be masked independently.

## Analog to Digital Converter – ADC

- 12-bit SAR ADC engine

- Up to 1 Msps conversion rate

- Up to 8 external analog input channels

A 12-bit multi-channel ADC is integrated in the device. There are multiplexed channels, which include 8 external analog signal channels and 2 internal channels which can be measured. If the input voltage is required to remain within a specific threshold window, an Analog Watchdog function will monitor and detect these signals. An interrupt will then be generated to inform the device that the input voltage is not within the preset threshold levels. There are three conversion modes to convert an analog signal to digital data. The ADC can be operated in one shot, continuous and discontinuous conversion modes.

## I/O Ports – GPIO

- Up to 21 GPIOs

- Port A, B are mapped as 16 external interrupts EXTI

- Almost all I/O pins have a configurable output driving current

There are up to 21 General Purpose I/O pins, GPIO, named Port A and Port B for the implementation of logic input/output functions. Each of the GPIO ports has a series of related control and configuration registers to maximize flexibility and to meet the requirements of a wide range of applications.

The GPIO ports are pin-shared with other alternative functions to obtain maximum functional flexibility on the package pins. The GPIO pins can be used as alternative functional pins by configuring the corresponding registers regardless of the input or output pins. The external interrupts on the GPIO pins of the device have related control and configuration registers in the External Interrupt Control Unit, EXTI.

## **General-Purpose Timer – GPTM**

- 16-bit up, down, up/down auto-reload counter

- Up to 4 independent channels

- 16-bit programmable prescaler that allows division of the prescaler clock source by any factor between 1 and 65536 to generate the counter clock frequency

- Input Capture function

- Compare Match Output

- PWM waveform generation with Edge-aligned and Center-aligned Counting Modes

- Single Pulse Mode Output

- Encoder interface controller with two inputs using quadrature decoder

The General-Purpose Timer Module consists of one 16-bit up/down-counter, four 16-bit Capture/ Compare Registers (CCRs), one 16-bit Counter Reload Register (CRR) and several control/status registers. They can be used for a variety of purposes including general time measurement, input signal pulse width measurement, output waveform generation such as single pulse generation, or PWM output generation. The GPTM supports an Encoder Interface using a decoder with two inputs.

## Single Channel Timer – SCTM

- 16-bit up and auto-reload counter

- One channel for each timer

- 16-bit programmable prescaler that allows division of the prescaler clock source by any factor between 1 and 65536 to generate the counter clock frequency

- Input Capture function

- Compare Match Output

- PWM waveform generation with Edge-aligned

The Single-Channel Timer consists of one 16-bit up-counter, one 16-bit Capture/Compare Register (CCR), one 16-bit Counter-Reload Register (CRR) and several control/status registers. It can be used for a variety of purposes including general timer, input signal pulse width measurement or output waveform generation such as single pulse generation or PWM output.

## **Basic Function Timer – BFTM**

- 32-bit compare/match count-up counter no I/O control

- One shot mode counter stops counting when compare match occurs

- Repetitive mode counter restarts when compare match occurs

The Basic Function Timer is a simple count-up 32-bit counter designed to measure time intervals and generate a one shot or repetitive interrupts. The BFTM operates in two functional modes, repetitive or one shot mode. In the repetitive mode the BFTM restarts the counter when a compare match event occurs. The BFTM also supports a one shot mode which forces the counter to stop counting when a compare match event occurs.

## Watchdog Timer – WDT

- 12-bit down counter with 3-bit prescaler

- Provide reset to the system

- Programmable watchdog timer window function

- Register write protection function

The Watchdog Timer is a hardware timing circuit that can be used to detect system failures due to software malfunctions. It includes a 12-bit count-down counter, a prescaler, a WDT delta value register, WDT operation control circuitry and a WDT protection mechanism. If the software does not reload the counter value before a Watchdog Timer underflow occurs, a reset will be generated when the counter underflows. In addition, a reset is also generated if the software reloads the counter when the counter value is greater than the WDT delta value. This means the counter must be reloaded within a limited timing window using a specific method. The Watchdog Timer counter can be stopped while the processor is in the debug mode. There is a register write protect function which can be enabled to prevent it from changing the Watchdog Timer configuration unexpectedly.

## Inter-integrated Circuit – I<sup>2</sup>C

- Supports both master and slave modes with a frequency of up to 1 MHz

- Provides an arbitration function and clock synchronization

- Supports 7-bit and 10-bit addressing modes and general call addressing

- Supports slave multi-addressing mode with maskable address

The I<sup>2</sup>C is an internal circuit allowing communication with an external I<sup>2</sup>C interface which is an industry standard two line serial interface used for connection to external hardware. These two serial lines are known as a serial data line, SDA, and a serial clock line, SCL. The I<sup>2</sup>C module provides three data transfer rates: 100 kHz in the Standard mode, 400 kHz in the Fast mode and 1 MHz in the Fast plus mode. The SCL period generation register is used to setup different kinds of duty cycle implementations for the SCL pulse.

The SDA line which is connected directly to the  $I^2C$  bus is a bi-directional data line between the master and slave devices and is used for data transmission and reception. The  $I^2C$  also has an arbitration detect function and clock synchronization to prevent situations where more than one master attempts to transmit data to the  $I^2C$  bus at the same time.

## Serial Peripheral Interface – SPI

- Supports both master and slave modes

- Frequency of up to  $(f_{PCLK}/2)$  MHz for the master mode and  $(f_{PCLK}/3)$  MHz for the slave mode

- FIFO Depth: 8 levels

- Multi-master and multi-slave operation

The Serial Peripheral Interface, SPI, provides an SPI protocol data transmit and receive function in both master and slave mode. The SPI interface uses 4 pins, which are the serial data input and output lines MISO and MOSI, the clock line, SCK, and the slave select line, SEL. One SPI device acts as a master device which controls the data flow using the SEL and SCK signals to indicate the start of data communication and the data sampling rate. To receive a data byte, the streamed data bits are latched on a specific clock edge and stored in the data register or in the RX FIFO. Data transmission is carried out in a similar way but in a reverse sequence. The mode fault detection provides a capability for multi-master applications.

## **Universal Synchronous Asynchronous Receiver Transmitter – USART**

- Supports both asynchronous and clocked synchronous serial communication modes

- Programmable baud rate clock frequency up to (f<sub>PCLK</sub>/16) MHz for Asynchronous mode and (f<sub>PCLK</sub>/8) MHz for synchronous mode

- Full duplex communication

- Fully programmable serial communication characteristics including:

- Word length: 7, 8, or 9-bit character

- Parity: Even, odd, or no-parity bit generation and detection

- Stop bit: 1 or 2 stop bit generation

- Bit order: LSB-first or MSB-first transfer

- Error detection: Parity, overrun and frame error

- Auto hardware flow control mode RTS, CTS

- IrDA SIR encoder and decoder

- RS485 mode with output enable control

- FIFO Depth: 8-level for both receiver and transmitter

The Universal Synchronous Asynchronous Receiver Transceiver, USART, provides a flexible full duplex data exchange using synchronous or asynchronous data transfer. The USART is used to translate data between parallel and serial interfaces, and is commonly used for RS232 standard communication. The USART peripheral function supports four types of interrupt including Line Status Interrupt, Transmitter FIFO Empty Interrupt, Receiver Threshold Level Reaching Interrupt and Time Out Interrupt. The USART module includes a transmitter FIFO, (TX\_FIFO) and receiver

FIFO (RX\_FIFO). The software can detect a USART error status by reading the USART Status & Interrupt Flag Register, USRSIFR. The status includes the type and the condition of transfer operations as well as several error conditions resulting from Parity, Overrun, Framing and Break events.

## **Universal Asynchronous Receiver Transmitter – UART**

- $\blacksquare$  Asynchronous serial communication operating baud-rate clock frequency up to (f<sub>PCLK</sub>/16) MHz

- Full duplex communication

- Fully programmable serial communication characteristics including:

- Word length: 7, 8, or 9-bit character

- Parity: Even, odd, or no-parity bit generation and detection

- Stop bit: 1 or 2 stop bit generation

- Bit order: LSB-first or MSB-first transfer

- Error detection: Parity, overrun and frame error

The Universal Asynchronous Receiver Transceiver, UART, provides a flexible full duplex data exchange using asynchronous transfer. The UART is used to translate data between parallel and serial interfaces, and is commonly used for RS232 standard communication. The UART peripheral function supports Line Status Interrupt. The software can detect a UART error status by reading the UART Status & Interrupt Flag Register, URSIFR. The status includes the type and the condition of transfer operations as well as several error conditions resulting from Parity, Overrun, Framing and Break events.

## **RF Module**

- Frequency band: 315/433/470/868/915 MHz

- OOK/FSK/GFSK modulation

- Supports 3-wire or 4-wire SPI interface

- Programmable data rate:

- $\bullet$  OOK: 0.5 Kbps  $\sim 20$  Kbps

- GFSK: 2 Kbps ~ 250 Kbps

- Programmable TX output power: up to 20 dBm

- Low current consumption

- $\bullet$  0.4  $\mu A$  deep sleep mode current with data retention

- RX current consumption (AGC on & low data rate) @ 433.92 MHz: 5.9 mA

- RX current consumption (AGC on & low data rate) @ 868.3 MHz: 6.9 mA

- TX current consumption @ 433.92 MHz: 33 mA @ 10 dBm Pout

- TX current consumption @ 868.3 MHz: 35 mA @ 10 dBm Pout

- High RX sensitivity (433.92 MHz)

- -117 dBm at 2 Kbps on-air data rate

- -100 dBm at 250 Kbps on-air data rate

- High RX sensitivity (868.3 MHz)

- -116 dBm at 2 Kbps on-air data rate

- -100 dBm at 250 Kbps on-air data rate

- On-chip VCO and Fractional-N synthesizer with integrated loop filter

- Supports low cost 16 MHz crystal with integrated load capacitor

- AGC (Auto Gain Control) to achieve wide input range, up to +10 dBm

- AFC (Auto Frequency Compensation) for frequency drift due to X'tal aging

- On-chip low power RC oscillator for WOR (Wake-on-RX) and WOT (Wake-on-TX) functions

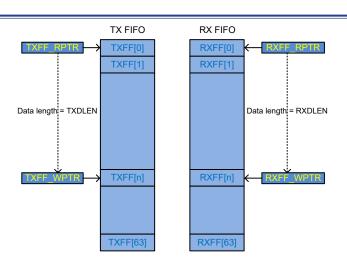

- Physical TX/RX FIFO buffers: TX 64 bytes, RX 64 bytes

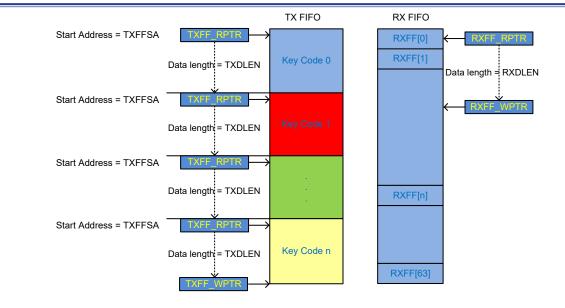

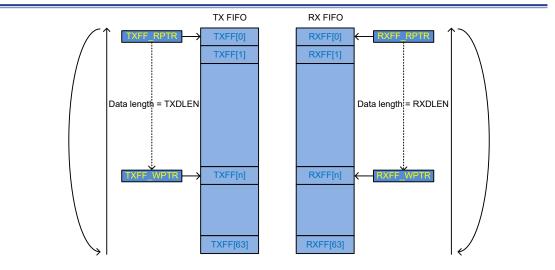

- Simple FIFO/Block FIFO/Extend FIFO (up to 255 bytes)/Infinite FIFO modes

- Programmable threshold for carrier detection

- Frame synchronization recognition for both FIFO mode and Direct mode

- Packet handling

- FEC (Forward Error Correction)

- Data whitening

- Manchester encoding

- CRC-16 checking

- ATR (Auto-Transmit-Receive)

- Auto-resend

- Auto-acknowledgment

- WOT + Auto-resend

- WOR + Auto-acknowledgment

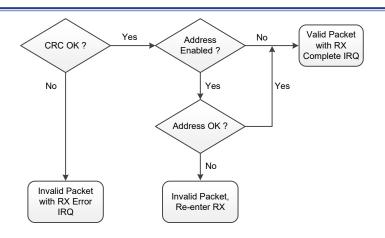

- Packet filtering

- CRC filtering

- Address filtering

## **Debug Support**

- Serial Wire Debug Port SW-DP

- 4 comparators for hardware breakpoint or code / literal patch

- 2 comparators for hardware watchpoints

## Package and Operation Temperature

- 46-pin QFN package

- Operation temperature range: -40 °C to 85 °C

# **3** Overview

## **Device Information**

| Table 1. | Features | and | Peripheral | List |

|----------|----------|-----|------------|------|

|----------|----------|-----|------------|------|

| Periphe                   | erals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | HT32F67233               |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Main Flash (KB)           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                       |

| Option Bytes Flash (KB)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                        |

| SRAM (KB)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                        |

|                           | GPTM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                        |

| Timers                    | SCTM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                        |

| Timers                    | BFTM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                        |

|                           | GPTM         SCTM         BFTM         WDT         SPI         USART         UART         I <sup>2</sup> C         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I | 1                        |

|                           | SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                        |

| Communication             | USART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                        |

| Communication             | UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                        |

|                           | I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                        |

| EXTI                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16                       |

| 12-bit ADC                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                        |

| Number of channels        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8 Channels               |

| GPIO                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Up to 21                 |

| RF frequency bands        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 315/433/470/868/915 MHz  |

| Modulation type           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OOK/GFSK                 |

| Dragrammable data rata    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.5 ~ 50 Kbps (OOK mode) |

| Programmable data rate    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2 ~ 250 Kbps (GFSK mode) |

| Max. output power         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 dBm                   |

| RF RX current consumption |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.9 mA @ 433 MHz         |

|                           | Л                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.9 mA @ 868 MHz         |

| DV consitivity            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -117 dBm @ 433 MHz       |

| RX sensitivity            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -116 dBm @ 868 MHz       |

| CPU frequency             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Up to 40 MHz             |

| Operating voltage         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.0 V ~ 3.6 V            |

| Operating temperature     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -40 °C ~ 85 °C           |

| Package                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46-pin QFN               |

Note: The functions listed here, except the Sub-1 GHz GFSK RF transceiver, are compatible with the HT32F52230 device. Refer to the HT32F52230 user manual for detailed function description.

## **Block Diagram**

## **Memory Map**

Figure 2. Memory Map

ω

| Start Address           0x4000_0000           0x4000_1000           0x4000_2000           0x4000_4000 | End Address<br>0x4000_0FFF<br>0x4000_1FFF<br>0x4000_3FFF<br>0x4000_4FFF | Peripheral<br>USART<br>UART<br>Reserved | Bus |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|-----|

| 0x4000_1000<br>0x4000_2000                                                                            | 0x4000_1FFF<br>0x4000_3FFF                                              | UART                                    |     |

| 0x4000_2000                                                                                           | 0x4000_3FFF                                                             | _                                       |     |

|                                                                                                       |                                                                         | Reserved                                | 1   |

| 0x4000 4000                                                                                           | 0x4000 4FFF                                                             |                                         |     |

|                                                                                                       |                                                                         | SPI                                     |     |

| 0x4000_5000                                                                                           | 0x4000_FFFF                                                             | Reserved                                |     |

| 0x4001_0000                                                                                           | 0x4001_0FFF                                                             | ADC                                     |     |

| 0x4001_1000                                                                                           | 0x4002_1FFF                                                             | Reserved                                |     |

| 0x4002_2000                                                                                           | 0x4002_2FFF                                                             | AFIO                                    |     |

| 0x4002_3000                                                                                           | 0x4002_3FFF                                                             | Reserved                                |     |

| 0x4002_4000                                                                                           | 0x4002_4FFF                                                             | EXTI                                    |     |

| 0x4002_5000                                                                                           | 0x4003_3FFF                                                             | Reserved                                |     |

| 0x4003_4000                                                                                           | 0x4003_4FFF                                                             | SCTM0                                   |     |

| 0x4003_5000                                                                                           | 0x4004_7FFF                                                             | Reserved                                | APB |

| 0x4004_8000                                                                                           | 0x4004_8FFF                                                             | I <sup>2</sup> C                        |     |

| 0x4004_9000                                                                                           | 0x4006_7FFF                                                             | Reserved                                |     |

| 0x4006_8000                                                                                           | 0x4006_8FFF                                                             | WDT                                     |     |

| 0x4006_9000                                                                                           | 0x4006_9FFF                                                             | Reserved                                |     |

| 0x4006_A000                                                                                           | 0x4006_AFFF                                                             | PWRCU                                   |     |

| 0x4006_B000                                                                                           | 0x4006_DFFF                                                             | Reserved                                |     |

| 0x4006_E000                                                                                           | 0x4006_EFFF                                                             | GPTM                                    |     |

| 0x4006_F000                                                                                           | 0x4007_3FFF                                                             | Reserved                                |     |

| 0x4007_4000                                                                                           | 0x4007_4FFF                                                             | SCTM1                                   |     |

| 0x4007_5000                                                                                           | 0x4007_5FFF                                                             | Reserved                                |     |

| 0x4007_6000                                                                                           | 0x4007_6FFF                                                             | BFTM                                    |     |

| 0x4007_7000                                                                                           | 0x4007_FFFF                                                             | Reserved                                |     |

| 0x4008_0000                                                                                           | 0x4008_1FFF                                                             | FMC                                     |     |

| 0x4008_2000                                                                                           | 0x4008_7FFF                                                             | Reserved                                |     |

| 0x4008_8000                                                                                           | 0x4008_9FFF                                                             | CKCU & RSTCU                            |     |

| 0x4008_A000                                                                                           | 0x400A_FFFF                                                             | Reserved                                | AHB |

| 0x400B_0000                                                                                           | 0x400B_1FFF                                                             | GPIOA                                   |     |

| 0x400B_2000                                                                                           | 0x400B_3FFF                                                             | GPIOB                                   |     |

| 0x400B_4000                                                                                           | 0x400F_FFFF                                                             | Reserved                                |     |

#### Table 2. Register Map

## **Clock Structure**

# **4 RF Module**

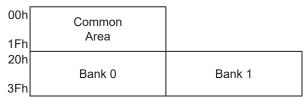

## **Memory Mapping**

Common Area: It contains 32 bytes space. Accessing addresses  $00h \sim 1Fh$  always means to access the Common Area regardless of Bank Pointer configuration.

Bank  $0 \sim 1$ : Each bank contains 32 bytes space. They are selected by the Bank Pointer.

The Bank Pointer, BANK[1:0], which is defined in the Common Area, can be set directly by the Set Register Bank command and read/written by the Control Register command.

## **Control Register Access**

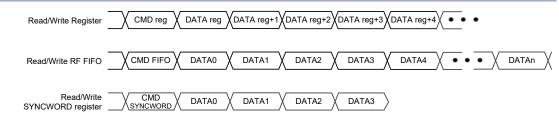

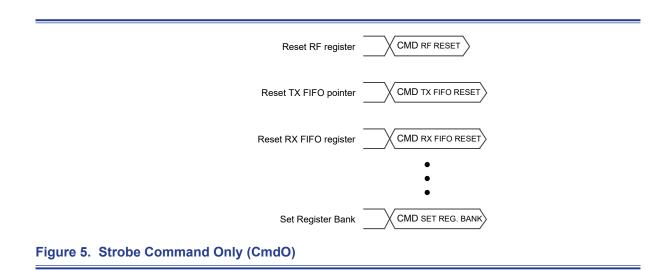

Figure 4. Strobe Command Followed by n-byte Data (CmdD)

## **SFR Mapping and Bit Definition**

#### **Common Area Control Register**