# HT16C22A/HT16C22AG RAM Mapping 44×4 LCD Controller Driver

#### **Features**

Operating voltage: 2.4V~5.5VInternal 32kHz RC oscillator

• Bias: 1/2 or 1/3; Duty: 1/4

Internal LCD bias generation with voltage-follower buffers

• I<sup>2</sup>C bus interface

• Two selectable LCD frame frequencies: 80Hz or 160Hz

• Up to 44×4 bits RAM for display data storage

• Max. 44×4 patterns: 44 segments and 4 commons

• Versatile blinking modes

· R/W address auto increment

Internal 16-step voltage adjustment to adjust LCD operating voltage

• Low power consumption

• Provides the VLCD pin to adjust LCD operating voltage

· Manufactured in silicon gate CMOS process

• Package Types: 48/52-pin LQFP and COG

# **Applications**

- · Electronic meter

- · Water meter

- · Gas meter

- · Heat energy meter

- · Household appliance

- Games

- Telephone

- · Consumer electronics

## **General Description**

The HT16C22A/HT16C22AG devices are a memory mapping and multi-function LCD controller driver. The maximum display segments of the devices are 176 patterns (44 segments and 4 commons). The software configuration feature of the HT16C22A/HT16C22AG devices make it suitable for multiple LCD applications including LCD modules and display subsystems. The HT16C22A/HT16C22AG devices communicate with most microprocessors/microcontrollers via a two-line bidirectional I²C bus.

#### **Selection Table**

| Part No.            | VDD       | Max. Resolution<br>Segment × Common | LCD<br>Voltage    | Bias     | Interface        | Package   |

|---------------------|-----------|-------------------------------------|-------------------|----------|------------------|-----------|

| HT16C22A            | 2.4V~5.5V | 44×4                                | < \/-             | 1/2. 1/3 | I <sup>2</sup> C | 48/52LQFP |

| HT16C22AG 2.4V~5.5V |           | 44^4                                | ≤ V <sub>DD</sub> | 1/2, 1/3 | 1-0              | Gold Bump |

Rev. 1.30 1 August 26, 2022

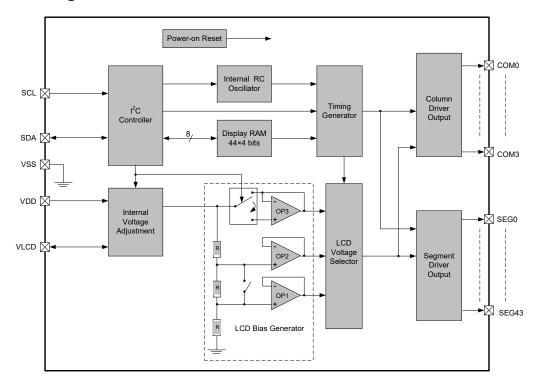

# **Block Diagram**

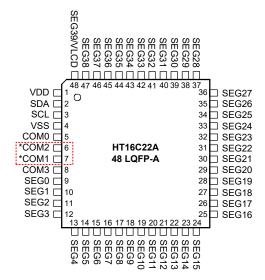

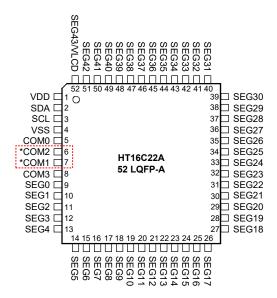

## **Pin Assignment**

Note: The \*COM1 and \*COM2 pins are not in sequential order.

Rev. 1.30 2 August 26, 2022

Note: The \*COM1 and \*COM2 pins are not in sequential order.

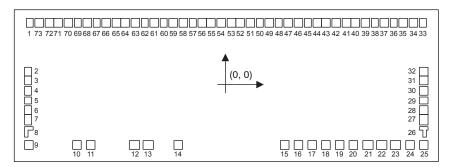

# **Pad Assignment for COG**

#### Note:

|        | ge Adjustment<br>Command | VLCD Segment43<br>(PAD14) (PAD5) |        | Note                                                                                         |

|--------|--------------------------|----------------------------------|--------|----------------------------------------------------------------------------------------------|

| DE Bit | VE Bit                   | (PAD14)                          | (PAD5) |                                                                                              |

| 0      | 0                        | Input                            | Null   | The VLCD input voltage can be smaller than or equal to VDD                                   |

| 0      | 1                        | Output                           | Null   | The VLCD pin is an output pin of which the voltage can be detected by the external MCU host. |

| 1      | 0                        | Null                             | Output | _                                                                                            |

| 1      | 1                        | Null                             | Output | _                                                                                            |

Rev. 1.30 3 August 26, 2022

# **Pad Dimensions for COG**

| Item           | Nun        | a la a u   | Si   | ze  | Unit |

|----------------|------------|------------|------|-----|------|

| item           | Nun        | iber       | X    | Y   | Unit |

| Chip size      | _          | _          | 2656 | 938 | μm   |

| Chip thickness | _          | _          | 50   | 08  | μm   |

| Pad pitch      | 1~7, 2     | 27~73      | 6    | 0   | μm   |

|                | 9~         | 25         | 8    | μm  |      |

|                | Output pad | 34~73      | 40   | 60  | μm   |

|                | Output pad | 2~5, 29~32 | 60   | 40  | μm   |

| Burns size     | Input pad  | 10~14      | 67   | 67  | μm   |

| Bump size      |            | 1, 33      | 40   | 60  | μm   |

|                | Dummy pad  | 6~7, 27~28 | 60   | 40  | μm   |

|                |            | 9, 15~25   | 67   | 67  | μm   |

| Bump height    | All pad    |            | 18±3 |     | μm   |

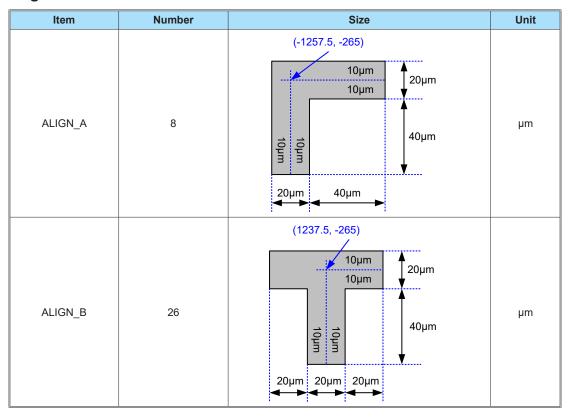

# **Alignment Mark Dimensions for COG**

Rev. 1.30 4 August 26, 2022

# **Pad Coordinates for COG**

Unit: µm

| No | Name  | Х       | Υ       | No | Name  | Х     | Υ     |

|----|-------|---------|---------|----|-------|-------|-------|

| 1  | DUMMY | -1230   | 379 .5  | 39 | SEG5  | 870   | 379.5 |

| 2  | SEG40 | -1238.5 | 86.25   | 40 | SEG6  | 810   | 379.5 |

| 3  | SEG41 | -1238.5 | 26.25   | 41 | SEG7  | 750   | 379.5 |

| 4  | SEG42 | -1238.5 | -33.75  | 42 | SEG8  | 690   | 379.5 |

| 5  | SEG43 | -1238.5 | -93.75  | 43 | SEG9  | 630   | 379.5 |

| 6  | DUMMY | -1238.5 | -153.75 | 44 | SEG10 | 570   | 379.5 |

| 7  | DUMMY | -1238.5 | -213.75 | 45 | SEG11 | 510   | 379.5 |

| 9  | DUMMY | -1235   | -370.4  | 46 | SEG12 | 450   | 379.5 |

| 10 | SDA   | -933    | -370.4  | 47 | SEG13 | 390   | 379.5 |

| 11 | SCL   | -846    | -370.4  | 48 | SEG14 | 330   | 379.5 |

| 12 | VDD   | -575    | -370.4  | 49 | SEG15 | 270   | 379.5 |

| 13 | VSS   | -488    | -370.4  | 50 | SEG16 | 210   | 379.5 |

| 14 | VLCD  | -300    | -370.4  | 51 | SEG17 | 150   | 379.5 |

| 15 | DUMMY | 365     | -370.4  | 52 | SEG18 | 90    | 379.5 |

| 16 | DUMMY | 452     | -370.4  | 53 | SEG19 | 30    | 379.5 |

| 17 | DUMMY | 539     | -370.4  | 54 | SEG20 | -30   | 379.5 |

| 18 | DUMMY | 626     | -370.4  | 55 | SEG21 | -90   | 379.5 |

| 19 | DUMMY | 713     | -370.4  | 56 | SEG22 | -150  | 379.5 |

| 20 | DUMMY | 800     | -370.4  | 57 | SEG23 | -210  | 379.5 |

| 21 | DUMMY | 887     | -370.4  | 58 | SEG24 | -270  | 379.5 |

| 22 | DUMMY | 974     | -370.4  | 59 | SEG25 | -330  | 379.5 |

| 23 | DUMMY | 1061    | -370.4  | 60 | SEG26 | -390  | 379.5 |

| 24 | DUMMY | 1148    | -370.4  | 61 | SEG27 | -450  | 379.5 |

| 25 | DUMMY | 1235    | -370.4  | 62 | SEG28 | -510  | 379.5 |

| 27 | DUMMY | 1238.5  | -213.75 | 63 | SEG29 | -570  | 379.5 |

| 28 | DUMMY | 1238.5  | -153.75 | 64 | SEG30 | -630  | 379.5 |

| 29 | COM0  | 1238.5  | -93.75  | 65 | SEG31 | -690  | 379.5 |

| 30 | COM1  | 1238.5  | -33.75  | 66 | SEG32 | -750  | 379.5 |

| 31 | COM2  | 1238.5  | 26.25   | 67 | SEG33 | -810  | 379.5 |

| 32 | COM3  | 1238.5  | 86.25   | 68 | SEG34 | -870  | 379.5 |

| 33 | DUMMY | 1230    | 379.5   | 69 | SEG35 | -930  | 379.5 |

| 34 | SEG0  | 1170    | 379.5   | 70 | SEG36 | -990  | 379.5 |

| 35 | SEG1  | 1110    | 379.5   | 71 | SEG37 | -1050 | 379.5 |

| 36 | SEG2  | 1050    | 379.5   | 72 | SEG38 | -1110 | 379.5 |

| 37 | SEG3  | 990     | 379.5   | 73 | SEG39 | -1170 | 379.5 |

| 38 | SEG4  | 930     | 379.5   |    |       |       |       |

# **Alignment Mark Coordinates for COG**

| No | Name    | Х       | Y    | No | Name    | Х      | Υ    |

|----|---------|---------|------|----|---------|--------|------|

| 8  | ALIGN A | -1257.5 | -265 | 26 | ALIGN B | 1237.5 | -265 |

Rev. 1.30 5 August 26, 2022

# **Pin Description**

| Pin Name   | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA        | I/O  | Serial Data Input/Output for I <sup>2</sup> C interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SCL        | I    | Serial Clock Input for I <sup>2</sup> C interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD        | _    | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VSS        | _    | Negative power supply, ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VLCD       | _    | <ul> <li>Power supply for LCD driver</li> <li>One external resistor is connected between the VLCD pin and the VDD pin to determine the bias voltage for packages with a VLCD pin. Internal voltage adjustment function is disabled.</li> <li>Internal voltage adjustment function can be used to adjust the V<sub>LCD</sub> voltage. If the VLCD pin is used as voltage detection pin, an external power supply should not be applied to the VLCD pin.</li> <li>An external MCU can detect the voltage of the VLCD pin and program the internal voltage adjustment for packages with a VLCD pin.</li> </ul> |

| COM0~COM3  | 0    | LCD Common outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SEG0~SEG43 | 0    | LCD Segment outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

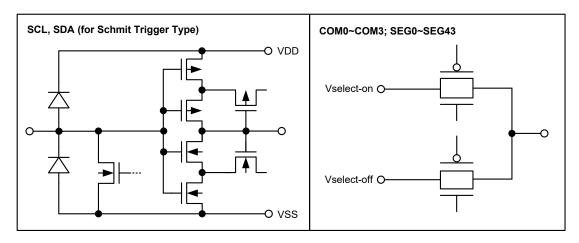

#### **Approximate Internal Connections**

# **Absolute Maximum Ratings**

| Supply Voltage $V_{\text{SS}}0.3V$ to $V_{\text{SS}}\text{+-}6.5V$ | Storage Temperature60°C to 150°C  |

|--------------------------------------------------------------------|-----------------------------------|

| Input Voltage $V_{SS}$ =0.3V to $V_{DD}$ +0.3V                     | Operating Temperature40°C to 85°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.30 6 August 26, 2022

# D.C. Characteristics

$V_{SS}$ =0V,  $V_{DD}$ =2.4V~5.5V,  $V_{LCD}$ =2.4V~5.5V, Ta=-40°C~85°C

| Courselle ed     | Parameter                  |                 | Test Conditions                                                                                | Min                | T    | May                | I I m i 4 |

|------------------|----------------------------|-----------------|------------------------------------------------------------------------------------------------|--------------------|------|--------------------|-----------|

| Symbol           | Parameter                  | V <sub>DD</sub> | Conditions                                                                                     | Min.               | Тур. | Max.               | Unit      |

| $V_{DD}$         | Operating Voltage          | _               | _                                                                                              | 2.4                | _    | 5.5                | V         |

| V <sub>LCD</sub> | Operating Voltage          | _               | _                                                                                              | 2.4                | _    | V <sub>DD</sub>    | V         |

|                  |                            | 3V              | No load, V <sub>LCD</sub> =V <sub>DD</sub> , 1/3 bias, f <sub>LCD</sub> =80Hz, LCD display on, | _                  | 18   | 27                 | μA        |

| I <sub>DD</sub>  | Operating Current          | 5V              | internal system oscillator on,<br>DA0~DA3 are set to "0000"                                    | _                  | 25   | 40                 | μA        |

| IDD              |                            | 3V              | No load, V <sub>LCD</sub> =V <sub>DD</sub> , 1/3 bias f <sub>LCD</sub> =80Hz, LCD display off, | _                  | 2    | 5                  | μA        |

|                  |                            | 5V              | internal system oscillator on, DA0~DA3 are set to "0000"                                       | _                  | 4    | 10                 | μΑ        |

| Іѕтв             | Standby Current            |                 | No load, V <sub>LCD</sub> =V <sub>DD</sub> , LCD display                                       | _                  | _    | 1                  | μΑ        |

| ISTB             | Standby Current            | 5V              | off, internal system oscillator off                                                            | _                  | _    | 2                  | μΑ        |

| VIH              | Input High Voltage         | _               | SDA, SCL                                                                                       | 0.7V <sub>DD</sub> | _    | V <sub>DD</sub>    | V         |

| V <sub>IL</sub>  | Input Low Voltage          | _               | SDA, SCL                                                                                       | 0                  | _    | 0.3V <sub>DD</sub> | V         |

| IIL              | Input Leakage Current      | _               | V <sub>IN</sub> =V <sub>SS</sub> or V <sub>DD</sub>                                            | -1                 | _    | 1                  | μΑ        |

| I <sub>OL</sub>  | Low Level Output Current   | 3V              | V <sub>OL</sub> =0.4V on SDA pin                                                               | 3                  | _    | _                  | mA        |

| IOL              | Low Level Output Current   | 5V              | VOL=0.4V OII SDA PIII                                                                          | 6                  | _    | _                  | mA        |

| I <sub>OL1</sub> | LCD Common Sink Current    | 3V              | V <sub>LCD</sub> =3V, V <sub>OL</sub> =0.3V                                                    | 250                | 400  | _                  | μΑ        |

| IOL1             | LCD Common Sink Current    | 5V              | V <sub>LCD</sub> =5V, V <sub>OL</sub> =0.5V                                                    | 500                | 800  | _                  | μΑ        |

|                  | LCD Common Course Current  | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V                                                    | -140               | -230 | _                  | μA        |

| I <sub>OH1</sub> | LCD Common Source Current  |                 | V <sub>LCD</sub> =5V, V <sub>OH</sub> =4.5V                                                    | -300               | -500 | _                  | μA        |

|                  | LCD Segment Sink Current   |                 | V <sub>LCD</sub> =3V, V <sub>OL</sub> =0.3V                                                    | 250                | 400  | _                  | μA        |

| I <sub>OL2</sub> |                            |                 | V <sub>LCD</sub> =5V, V <sub>OL</sub> =0.5V                                                    | 500                | 800  | _                  | μA        |

|                  | LOD Comment Course Course  | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V                                                    | -140               | -230 | _                  | μA        |

| I <sub>OH2</sub> | LCD Segment Source Current | 5V              | V <sub>LCD</sub> =5V, V <sub>OH</sub> =4.5V                                                    | -300               | -500 | _                  | μA        |

# A.C. Characteristics

$V_{\text{SS}}\text{=}0\text{V},\,V_{\text{DD}}\text{=}2.4\text{V}\text{\sim}5.5\text{V},\,V_{\text{LCD}}\text{=}2.4\text{V}\text{\sim}5.5\text{V},\,\text{Ta}\text{=}-40^{\circ}\text{C}\text{\sim}85^{\circ}\text{C},\,\text{unless otherwise specified}$

| Cumbal            | Parameter                                                                 |                 | Test Conditions          | Min.   | Tim  | May  | Unit |

|-------------------|---------------------------------------------------------------------------|-----------------|--------------------------|--------|------|------|------|

| Symbol            | Parameter                                                                 | V <sub>DD</sub> | Conditions               | IVIII. | Тур. | Max. | Unit |

| f <sub>LCD1</sub> | 100 5                                                                     |                 | 1/4 duty, Ta=25°C        | 72     | 80   | 88   | Hz   |

|                   | LCD Frame Frequency                                                       | 4V              | 1/4 duty, Ta=-40°C~+85°C | 52     | 80   | 124  | Hz   |

| £                 | LOD France Francesco                                                      |                 | 1/4 duty, Ta=25°C        | 144    | 160  | 176  | Hz   |

| f <sub>LCD2</sub> | LCD Frame Frequency                                                       | 4V              | 1/4 duty, Ta=-40°C~+85°C | 104    | 160  | 248  | Hz   |

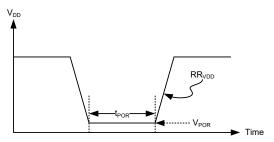

| V <sub>POR</sub>  | V <sub>DD</sub> Start Voltage to Ensure Power-on Reset                    | _               | _                        | _      | _    | 100  | mV   |

| RR <sub>VDD</sub> | V <sub>DD</sub> Rising Rate to Ensure Power-on Reset                      | _               | _                        | 0.05   | _    | _    | V/ms |

| t <sub>POR</sub>  | Minimum Time for $V_{DD}$ to Remain at $V_{POR}$ to Ensure Power-on Reset | _               | _                        | 10     | _    | _    | ms   |

Rev. 1.30 7 August 26, 2022

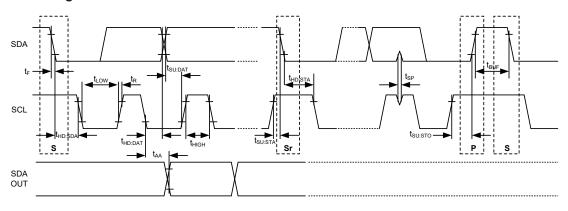

# I<sup>2</sup>C Interface A.C. Characteristics

Ta=-40°C~85°C

| O h l               | B                                             | 0 1141                                                                       | V <sub>DD</sub> =2.4 | IV~5.5V | V <sub>DD</sub> =3.0 | V~5.5V | 1114 |

|---------------------|-----------------------------------------------|------------------------------------------------------------------------------|----------------------|---------|----------------------|--------|------|

| Symbol              | Parameter                                     | Conditions                                                                   | Min.                 | Max.    | Min.                 | Max.   | Unit |

| f <sub>SCL</sub>    | Clock Frequency                               | _                                                                            | _                    | 100     | _                    | 400    | kHz  |

| t <sub>BUF</sub>    | Bus Free Time                                 | Time in which the bus<br>must be free before a new<br>transmission can start | 4.7                  | _       | 1.3                  | _      | μs   |

| t <sub>HD:STA</sub> | Start Condition Hold Time                     | After this period, the first clock pulse is generated                        | 4.0                  | _       | 0.6                  | _      | μs   |

| t <sub>LOW</sub>    | SCL Low Time                                  | _                                                                            | 4.7                  | _       | 1.3                  | _      | μs   |

| t <sub>HIGH</sub>   | SCL High Time                                 | _                                                                            | 4.0                  | _       | 0.6                  | _      | μs   |

| t <sub>su:sta</sub> | Start Condition Setup Time                    | Only relevant for repeated START condition                                   | 4.7                  | _       | 0.6                  | _      | μs   |

| t <sub>HD:DAT</sub> | Data Hold Time                                | _                                                                            | 0                    | _       | 0                    | _      | ns   |

| t <sub>SU:DAT</sub> | Data Setup Time                               | _                                                                            | 250                  | _       | 100                  | _      | ns   |

| t <sub>R</sub>      | SDA and SCL Rising Fime <sup>(Note)</sup>     | _                                                                            | _                    | 1.0     | _                    | 0.3    | μs   |

| t <sub>F</sub>      | SDA and SCL Falling Time(Note)                | _                                                                            | _                    | 0.3     | _                    | 0.3    | μs   |

| t <sub>su:sto</sub> | Stop Condition Setup Time                     | _                                                                            | 4.0                  | _       | 0.6                  | _      | μs   |

| t <sub>AA</sub>     | Output Valid from Clock                       | _                                                                            | _                    | 3.5     | _                    | 0.9    | μs   |

| t <sub>SP</sub>     | Input Filter Time Constant (SDA and SCL Pins) | Noise suppression time                                                       | _                    | 100     | _                    | 50     | ns   |

Note: These parameters are periodically sampled but not 100% tested.

# **Timing Diagrams**

# I<sup>2</sup>C Timing

Rev. 1.30 8 August 26, 2022

#### **Power-on Reset Timing**

The devices must be powered up under certain conditions to ensure correct operation as shown in the accompanying diagram.

Note that if the power-on reset timing conditions are not satisfied during the Power-on/off sequence, the internal power-on reset circuit will not operate normally. Also if  $V_{DD}$  drops below the minimum voltage of operating voltage specification during operation, the power-on reset timing conditions must be also satisfied. This means that  $V_{DD}$  must fall to 0V and remain at 0V for a minimum time of 10ms before rising to the normal operating voltage.

## **Functional Description**

#### **Power-on Reset**

When power is applied, the devices are initialised by an internal power-on reset circuit. The status of the internal circuits after initialisation is as follows:

- All common outputs are set to  $V_{\mbox{\tiny DD}}$

- All segment outputs are set to  $V_{\mbox{\tiny DD}}$

- The drive mode 1/4 duty output and 1/3 bias is selected

- The System Oscillator and the LCD bias generator are both off

- LCD Display is off

- · Internal voltage adjustment function is enabled

- · Detection switch for VLCD pin is disabled

- Frame Frequency is set to 80Hz

- · Blinking function is switched off

Data transfers on the I<sup>2</sup>C bus should be avoided for 1ms following power-on to allow completion of the reset action.

## **Display Memory - RAM Structure**

The display RAM is a static 44×4 bits RAM which stores LCD data. Logic "1" in the RAM bit-map indicates the "on" state of the corresponding LCD segment; similarly logic "0" indicates the "off" state.

The contents of the RAM data are directly mapped to the LCD data. The first RAM column corresponds to the 44 segments operated with respect to COM0. In multiplexed LCD applications the segment data of the second, third and fourth columns of the display RAM are time-multiplexed with COM1, COM2 and COM3 respectively. The following is a mapping from the RAM data to the LCD pattern:

| Output | СОМЗ | COM2 | COM1 | СОМО | Output | сомз | COM2 | COM1 | сомо | Address |

|--------|------|------|------|------|--------|------|------|------|------|---------|

| SEG1   |      |      |      |      | SEG0   |      |      |      |      | 00H     |

| SEG3   |      |      |      |      | SEG2   |      |      |      |      | 01H     |

| SEG5   |      |      |      |      | SEG4   |      |      |      |      | 02H     |

| SEG7   |      |      |      |      | SEG6   |      |      |      |      | 03H     |

| SEG9   |      |      |      |      | SEG8   |      |      |      |      | 04H     |

| SEG11  |      |      |      |      | SEG10  |      |      |      |      | 05H     |

| :      | :    | :    | :    | :    | :      | :    | :    | :    | :    | :       |

| :      | :    | :    | :    | :    | :      | :    | :    | :    | :    | :       |

| SEG43  |      |      |      |      | SEG42  |      |      |      |      | 15H     |

|        | D7   | D6   | D5   | D4   |        | D3   | D2   | D1   | D0   | Data    |

Display data transfer format for the I<sup>2</sup>C bus:

| MSB | MSB |    |    |    |    |    |    |  |

|-----|-----|----|----|----|----|----|----|--|

| D7  | D6  | D5 | D4 | D3 | D2 | D1 | D0 |  |

Rev. 1.30 9 August 26, 2022

#### **System Oscillator**

The timing for the internal logic and the LCD drive signals are generated by an internal oscillator. The system clock frequency ( $f_{sys}$ ) determines the LCD frame frequency. During initial system power-on the system oscillator will be in the stop state.

#### **LCD Bias Generator**

The full-scale LCD voltage  $(V_{op})$  is obtained from  $V_{\text{\tiny LCD}}-V_{\text{\tiny SS}}$ . The LCD voltage may be temperature compensated externally through the voltage supply to the VLCD pin.

Fractional LCD biasing voltages are obtained from an internal voltage divider of three series resistors connected between the VLCD and VSS pins. The centre resistor can be switched out of the circuits to provide a 1/2 bias voltage level for the 1/4 duty configuration.

#### **LCD Drive Mode Waveforms**

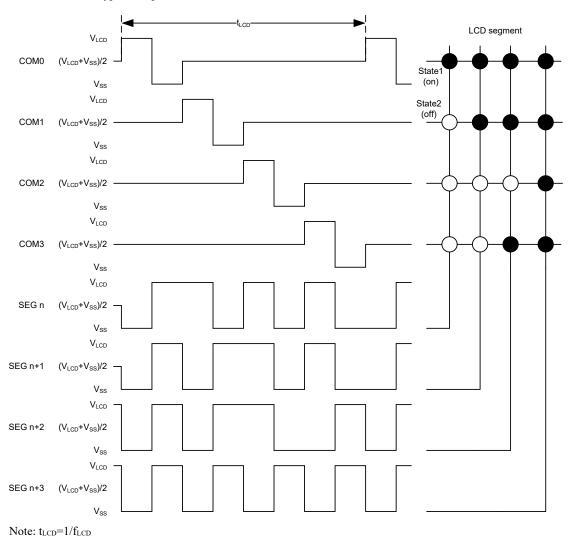

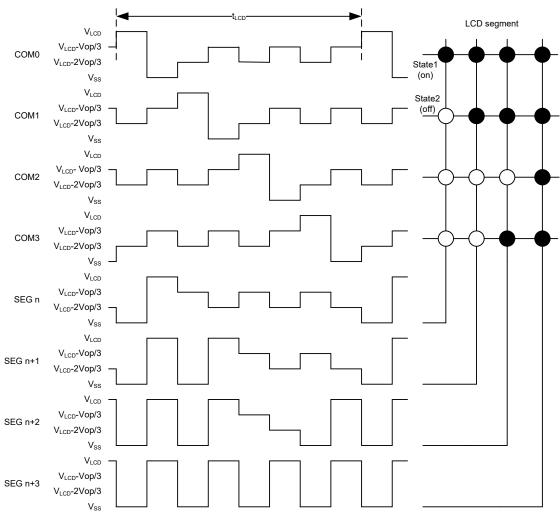

When four columns are provided in the LCD, the 1/4 duty drive mode applies. The HT16C22A/HT16C22AG can use 1/2 or 1/3 bias type in output waveforms as shown as follows:

Waveforms for 1/4 Duty Drive Mode with 1/2 Bias (Vop=VLCD-Vss)

Rev. 1.30 10 August 26, 2022

Note:  $t_{LCD}=1/f_{LCD}$

Waveforms for 1/4 Duty Drive Mode with 1/3 Bias (Vop=VLCD-Vss)

#### **Segment Driver Outputs**

The LCD drive section includes 44 segment outputs, SEG0~SEG43, which should be connected directly to the LCD panel. The segment output signals are generated in accordance with the multiplexed column signals and with the data resident in the display latch. When less than 44 segment outputs are required the unused segment outputs should be left open-circuit.

#### **Column Driver Outputs**

The LCD drive section includes 4 column outputs, COM0~COM3, which should be connected directly to the LCD panel. The column output signals are generated in accordance with the selected LCD drive mode. When less than 4 column outputs are required the unused column outputs should be left open-circuit.

#### **Address Pointer**

The addressing mechanism for the display RAM is implemented using the address pointer. This allows the loading of an individual display data byte, or a series of display data bytes, into any location of the display RAM. The sequence commences with the initialisation of the address pointer by the address pointer command.

Rev. 1.30 11 August 26, 2022

#### **Blinker Function**

The devices contain versatile blinking capabilities. The whole display can be blinked at a frequency selected by the Blink command. The blinking frequency is a subdivided ratio of the system frequency. The ratio between the system oscillator and blinking frequency depends on the blinking mode in which the devices are operating, as shown in the table:

| Blinking Mode | Operating Mode Ratio | Blinking Frequency (Hz) |

|---------------|----------------------|-------------------------|

| 0             | 0                    | Blink off               |

| 1             | fsys/ 16384          | 2                       |

| 2             | fsys / 32768         | 1                       |

| 3             | fsys / 65536         | 0.5                     |

#### **Frame Frequency**

The HT16C22A/HT16C22AG provide two frame frequencies selected with the Mode Setting command: 80Hz and 160Hz.

#### **V<sub>LCD</sub> Voltage Adjustment**

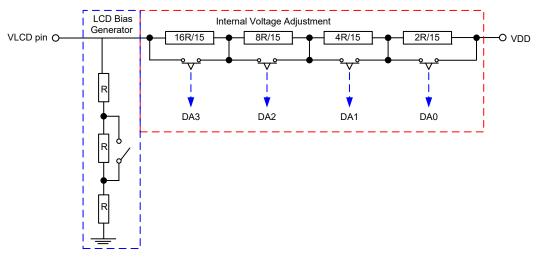

- The internal  $V_{\text{\tiny LCD}}$  adjustment contains four resistors in series and a 4-bit programmable analog switch which can provide sixteen voltage adjustment options using the  $V_{\text{\tiny LCD}}$  voltage adjustment command.

- The  $V_{\text{\tiny LCD}}$  adjustment structure is show in the diagram:

• The relationship between the programmable 4-bit analog switch and the  $V_{\mbox{\tiny LCD}}$  output voltage is shown in the table:

| DA3~DA0 | 1/2                    | 1/3                   | Note          |

|---------|------------------------|-----------------------|---------------|

| 00H     | 1.000×V <sub>DD</sub>  | 1.000×V <sub>DD</sub> | Default value |

| 01H     | 0.9375×V <sub>DD</sub> | 0.957×V <sub>DD</sub> | _             |

| 02H     | 0.882×V <sub>DD</sub>  | 0.918×V <sub>DD</sub> | _             |

| 03H     | 0.833×V <sub>DD</sub>  | 0.882×V <sub>DD</sub> | _             |

| 04H     | 0.789×V <sub>DD</sub>  | 0.849×V <sub>DD</sub> | _             |

| 05H     | 0.750×V <sub>DD</sub>  | 0.818×V <sub>DD</sub> | _             |

| 06H     | 0.714×V <sub>DD</sub>  | 0.789×V <sub>DD</sub> | _             |

| 07H     | 0.682×V <sub>DD</sub>  | 0.763×V <sub>DD</sub> | _             |

| 08H     | 0.652×V <sub>DD</sub>  | 0.738×V <sub>DD</sub> | _             |

| 09H     | 0.625×V <sub>DD</sub>  | 0.714×V <sub>DD</sub> | _             |

Rev. 1.30 12 August 26, 2022

| Bias<br>DA3~DA0 | 1/2                   | 1/3                   | Note |

|-----------------|-----------------------|-----------------------|------|

| 0AH             | 0.600×V <sub>DD</sub> | 0.692×V <sub>DD</sub> | _    |

| 0BH             | 0.577×V <sub>DD</sub> | 0.672×V <sub>DD</sub> | _    |

| 0CH             | 0.556×V <sub>DD</sub> | 0.652×V <sub>DD</sub> | _    |

| 0DH             | 0.536×V <sub>DD</sub> | 0.634×V <sub>DD</sub> | _    |

| 0EH             | 0.517×V <sub>DD</sub> | 0.616×V <sub>DD</sub> | _    |

| 0FH             | 0.500×V <sub>DD</sub> | 0.600×V <sub>DD</sub> | _    |

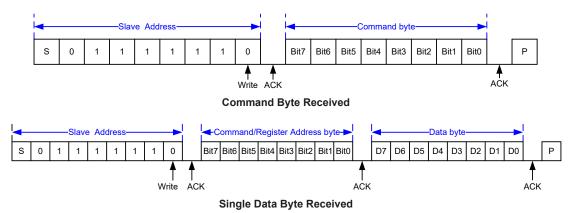

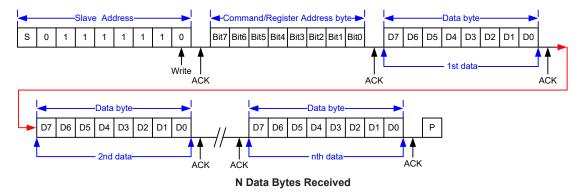

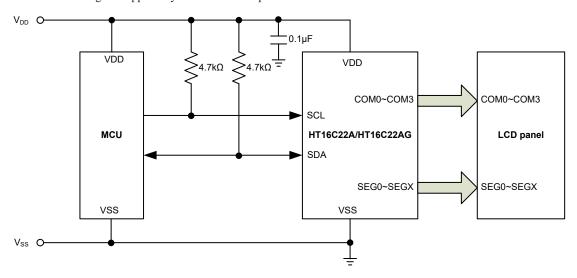

#### I<sup>2</sup>C Serial Interface

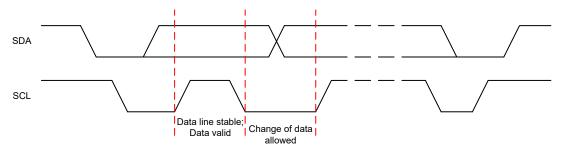

The devices include an I<sup>2</sup>C serial interface. The I<sup>2</sup>C bus is for bidirectional, two-line communication between different ICs or modules. The two lines are a serial data line, SDA, and a serial clock line, SCL. Both lines are connected to the positive supply via pull-up resistors with a typical value of  $4.7k\Omega$ . When the bus is free, both lines are high. Devices connected to the bus must have open-drain or open-collector outputs to implement a wired-or function. Data transfer is initiated only when the bus is not busy.

#### **Data Validity**

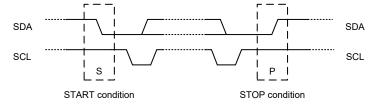

The data on the SDA line must be stable during the high period of the serial clock. The high or low state of the data line can only be changed when the clock signal on the SCL line is low as shown in the diagram.

#### **START and STOP Conditions**

- A high to low transition on the SDA line while SCL is high defines a START condition.

- A low to high transition on the SDA line while SCL is high defines a STOP condition.

- START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

- The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In some respects, the START (S) and repeated START (Sr) conditions are functionally identical.

Rev. 1.30 August 26, 2022

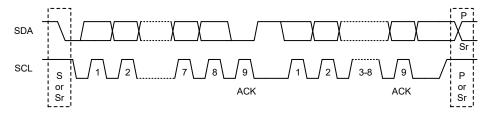

#### **Byte Format**

Every byte placed on the SDA line must be 8-bit in length. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit, MSB, first.

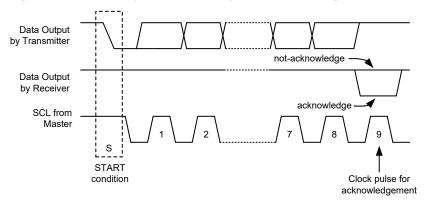

#### Acknowledge

- Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a low level placed on the bus by the receiver. The master generates an extra acknowledge related clock pulse.

- · A slave receiver which is addressed must generate an acknowledge bit, ACK, after the reception of each byte.

- The devices that acknowledge must pull down the SDA line during the acknowledge clock pulse so that it remains stable low during the high period of this clock pulse.

- A master receiver must signal an end of data to the slave by generating a not-acknowledge, NACK, bit on the last byte that has been clocked out of the slave. In this case, the master receiver must leave the data line high during the 9th pulse to not acknowledge. The master will generate a STOP or repeated START condition.

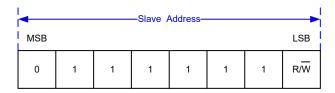

#### **Slave Addressing**

- The slave address byte is the first byte received following the START condition form the master device. The first seven bits of the first byte make up the slave address. The eighth bit defines a read or write operation to be performed. When the R/W bit is "1", a read operation is selected. A "0" selects a write operation.

- The HT16C22A/HT16C22AG address bits are "0111111". When an address byte is sent, the devices compare the first seven bits after the START condition. If they match, the devices output an acknowledge on the SDA line.

Rev. 1.30 14 August 26, 2022

#### **Write Operation**

#### **Byte Write Operation**

A byte write operation requires a START condition, a slave address with an  $R/\overline{W}$  bit, a valid Register Address, Data and a STOP condition. After each of the three bytes, the devices respond with an ACK.

Note: If the byte following the slave address is a command code, the byte following the command code will be ignored.

#### **Page Write Operation**

After a START condition the slave address with the  $R/\overline{W}$  bit is placed on the bus followed with the Register Address of which the contents are written to the internal address pointer. The data to be written to the memory will be transmitted next and then the internal address pointer will be increased by 1 to indicate the next memory address location after the reception of an acknowledge clock. After the internal address pointer reaches the maximum memory address, which is 15H, the address pointer will be reset to 00H.

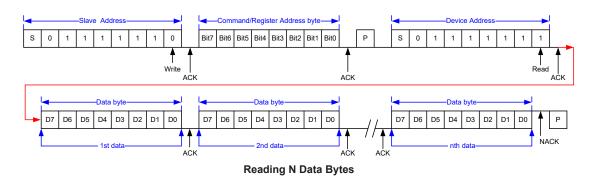

#### **Read Operation**

In this mode, the master reads the HT16C22A/HT16C22AG data after setting the slave address. Following the R/ $\overline{W}$  bit (="0") is an acknowledge bit and the Register Address (A<sub>N</sub>) which is written to the internal address pointer. After the start address of the Read Operation has been configured, another START condition and the slave address are transferred on the bus followed by the R/ $\overline{W}$  bit (="1"). Then the MSB of the data which was addressed is transmitted first on the I<sup>2</sup>C bus. The address pointer is only increased by 1 after the reception of an acknowledge clock. That means that if the devices are configured to transmit the data at the address of A<sub>N+1</sub>, the master will read and acknowledge the transferred new data byte and the internal address pointer is incremented to A<sub>N+2</sub>. After the internal address pointer reaches the maximum memory address which is 15H, the pointer will be reset to 00H.

This cycle of reading consecutive addresses will continue until the master sends a STOP condition.

Rev. 1.30 15 August 26, 2022

# **Command Summary**

#### **LCD Driver Setting Command**

This command is used to set the frame frequency output and internal system oscillator on/off and display on/off and driver mode.

| Function     | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | Def |

|--------------|---------------|------|------|------|------|------|------|---------------|------|-----|

| Mode Setting | 1             | 0    | 0    | F    | S    | Е    | 0    | MO            |      | 80H |

Note: 1. When "M0" is set to "0":

The driver mode is set to 1/3 bias.

2. When "M0" is set to "1":

The driver mode is set to 1/2 bias.

3. When "S" and "E" bits are set to {0, X}:

$Disable\ Internal\ System\ oscillator\ and\ display\ off.$

4. When "S" and "E" bits are set to {1, 0}: Enable Internal System oscillator and display off.

5. When "S" and "E" bits are set to  $\{1, 1\}$ :

Enable Internal System oscillator and display on.

6. When "F" bits is set to "0":

Frame Frequency=80Hz

7. When "F" bits is set to "1":

Frame Frequency=160Hz

8. Power-on status:

The drive mode 1/3 bias is selected.

Disable Internal System oscillator and display off.

Frame frequency is set to 80Hz.

9. If the programmed command data is not defined, the function will not be affected.

#### **Display Data Input Setting Command**

This command is used to send data from MCU to memory map of HT16C22A/HT16C22AG.

| Function        | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note                                     | Def |

|-----------------|---------------|------|------|------|------|------|------|---------------|------------------------------------------|-----|

| Address Pointer | 0             | 0    | 0    | A4   | А3   | A2   | A1   | A0            | Display data start address of memory map | 00H |

Note: 1. Power-on status: the address is set to 00H.

- 2. After reaching the memory location 15H, the pointer will reset to 00H.

- 3. If the programmed command data is not defined, the function will not be affected.

Rev. 1.30 16 August 26, 2022

#### **Blinking Setting Command**

This command is used to set the LCD blinking frequency of display modes.

| Function           | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note | Def |

|--------------------|---------------|------|------|------|------|------|------|---------------|------|-----|

| Blinking Frequency | 1             | 1    | 0    | 0    | 0    | 0    | BK1  | BK0           |      | C0H |

Note: 1. When "BK1" and "BK0" bits are set to  $\{0, 0\}$ :

Blinking off

2. When "BK1" and "BK0" bits are set to {0, 1}: Blinking Frequency = 2Hz

3. When "BK1" and "BK0" bits are set to  $\{1, 0\}$ : Blinking Frequency = 1Hz

4. When "BK1" and "BK0" bits are set to {1, 1}: Blinking Frequency = 0.5Hz

5. Power-on status: Blinking is switched off.

6. If the programmed command data is not defined, the function will not be affected.

#### Internal Voltage Adjustment (IVA) Setting Command

The internal voltage ( $V_{LCD}$ ) adjustment can provide sixteen kinds of regulator voltage adjustment options by setting LCD operating voltage adjustment command code.

| Function                           | (MSB)<br>Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | (LSB)<br>Bit0 | Note                                                                                                                                                                                                               | Def |

|------------------------------------|---------------|------|------|------|------|------|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Internal Voltage<br>Adjust Control | 0             | 1    | DE   | VE   | DA3  | DA2  | DA1  | DA0           | The Segment/VLCD shared pin can be programmed via the "DE" bit. The "VE" bit is used to enable or disable the internal voltage adjustment for bias voltage. DA3~DA0 can be used to adjust the VLCD output voltage. | 70H |

Note: 1. When "DE" and "VE" bits are set to  $\{0, 0\}$ :

The Segment/VLCD shared pin is set as the VLCD pin.

Disable the internal voltage adjustment.

One external resister must be connected between the VLCD pin and VDD pin to determine the bias voltage, and the internal voltage follower (OP3) must be enabled by setting DA3~DA0 to a value other than "0000". If the VLCD pin is connected to the VDD pin, the internal voltage follower (OP3) must be disabled by setting DA3~DA0 to "0000".

2. When "DE" and "VE" bits are set to  $\{0,1\}$ :

The Segment/VLCD shared pin is set as to the VLCD pin.

Enable the internal voltage adjustment.

The external MCU can detect the voltage of the VLCD pin.

3. When "DE" and "VE" bits are set to {1,0}:

The Segment/VLCD shared pin is set as the Segment pin.

Disable the internal voltage adjustment.

The bias voltage is supplied by the internal  $V_{\text{DD}}$  power.

The internal voltage follower (OP3) is disabled automatically when DE & VE is set to "10". DA3~DA0 don't care.

4. When "DE" and "VE" bits are set to  $\{1,1\}$ :

The Segment/VLCD shared pin is set as the Segment pin.

Enable the internal voltage adjustment.

- 5. When the DA0~DA3 bits are set to "0000", the internal voltage follower (OP3) is disabled. When DA0~DA3 bits are set to other values, the internal voltage follower (OP3) is enabled.

- 6. Power-on status: Enable the internal voltage adjustment and the Segment/VLCD pin is set as the Segment pin.

- 7. If the programmed command data is not defined, the function will not be affected.

Rev. 1.30 17 August 26, 2022

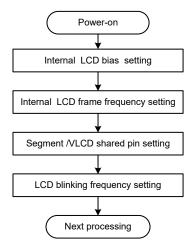

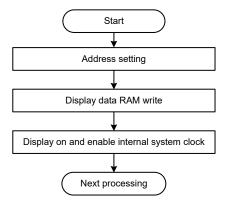

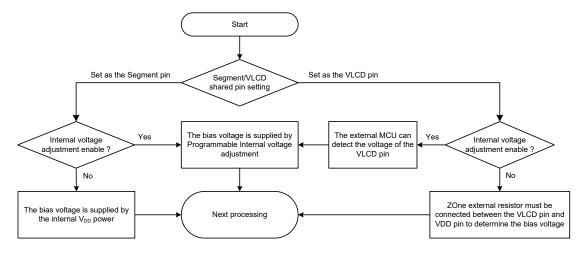

# **Operation FlowChart**

Access procedures are illustrated below by means of flowcharts.

#### Initialization

## **Display Data Read/Write (Address Setting)**

## Segment/VLCD Shared Pin Setting and Internal Voltage Adjustment Setting

Rev. 1.30 18 August 26, 2022

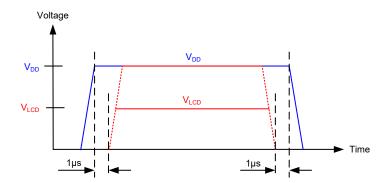

## **Power Supply Sequence**

- If the power is individually supplied on the VLCD and VDD pins, it is strongly recommended to follow the Holtek power supply sequence requirement.

- If the power supply sequence requirement is not followed, it may result in malfunction.

Holtek Power Supply Sequence Requirement:

- 1. Power-on sequence:

- Turn on the logic power supply V<sub>DD</sub> first and then turn on the LCD driver power supply V<sub>LCD</sub>.

- 2. Power-off sequence:

- Turn off the LCD driver power supply  $V_{\text{LCD}}$  first and then turn off the logic power supply  $V_{\text{DD}}$ .

When the  $V_{\text{LCD}}$  voltage is less than or is equal to  $V_{\text{DD}}$  voltage application:

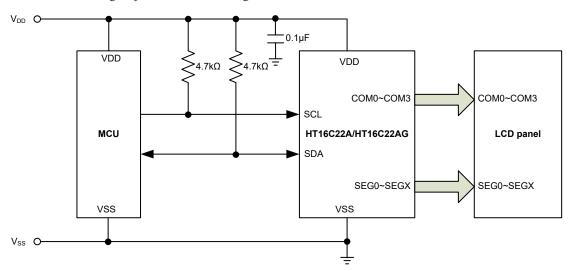

#### **Application Circuits**

#### Set as Segment Pin

#### Case 1:

- Disable the internal voltage adjustment.

- The bias voltage is supplied by the internal  $V_{\text{DD}}$  power.

Rev. 1.30 19 August 26, 2022

#### Case 2:

- Enable the internal voltage.

- The internal voltage adjustment for bias voltage.

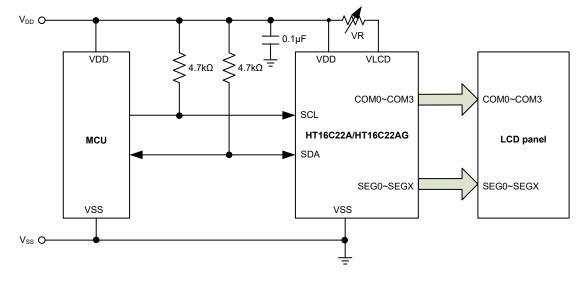

#### Set as VLCD Pin

#### Case 1:

- Disable the internal voltage adjustment.

- One external resister must be connected between the VLCD pin and VDD pin to determine the bias voltage.

Rev. 1.30 20 August 26, 2022

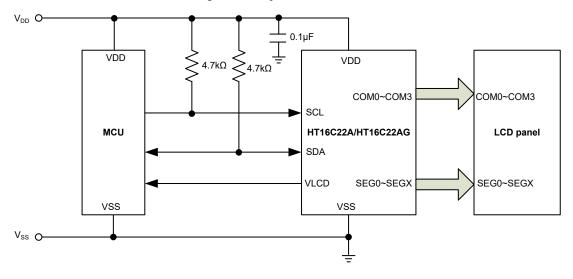

#### Case 2:

- Enable the internal voltage adjustment.

- The external MCU can detect the voltage of VLCD pin.

# **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Further Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- Packing Meterials Information

- Carton information

Rev. 1.30 22 August 26, 2022

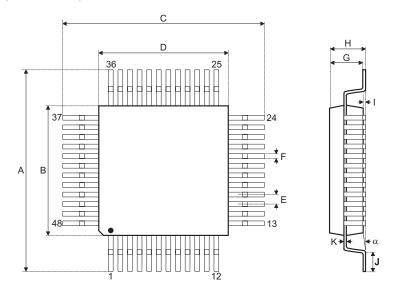

# 48-pin LQFP (7mm×7mm) Outline Dimensions

| Cumbal | Dimensions in inch |           |       |  |  |  |  |  |

|--------|--------------------|-----------|-------|--|--|--|--|--|

| Symbol | Min.               | Nom.      | Max.  |  |  |  |  |  |

| Α      | _                  | 0.354 BSC | _     |  |  |  |  |  |

| В      | _                  | 0.276 BSC | _     |  |  |  |  |  |

| С      | _                  | 0.354 BSC | _     |  |  |  |  |  |

| D      | _                  | 0.276 BSC | _     |  |  |  |  |  |

| E      | _                  | 0.020 BSC | _     |  |  |  |  |  |

| F      | 0.007              | 0.009     | 0.011 |  |  |  |  |  |

| G      | 0.053              | 0.055     | 0.057 |  |  |  |  |  |

| Н      | _                  | _         | 0.063 |  |  |  |  |  |

| I      | 0.002              | _         | 0.006 |  |  |  |  |  |

| J      | 0.018              | 0.024     | 0.030 |  |  |  |  |  |

| K      | 0.004              | _         | 0.008 |  |  |  |  |  |

| α      | 0°                 | _         | 7°    |  |  |  |  |  |

| Cumbal |      | Dimensions in mm |      |  |  |  |  |  |  |

|--------|------|------------------|------|--|--|--|--|--|--|

| Symbol | Min. | Nom.             | Max. |  |  |  |  |  |  |

| А      | _    | 9.00 BSC         | _    |  |  |  |  |  |  |

| В      | _    | 7.00 BSC         | _    |  |  |  |  |  |  |

| С      | _    | 9.00 BSC         | _    |  |  |  |  |  |  |

| D      | _    | 7.00 BSC         | _    |  |  |  |  |  |  |

| E      | _    | 0.50 BSC         | _    |  |  |  |  |  |  |

| F      | 0.17 | 0.22             | 0.27 |  |  |  |  |  |  |

| G      | 1.35 | 1.40             | 1.45 |  |  |  |  |  |  |

| Н      | _    | _                | 1.60 |  |  |  |  |  |  |

| 1      | 0.05 | _                | 0.15 |  |  |  |  |  |  |

| J      | 0.45 | 0.60             | 0.75 |  |  |  |  |  |  |

| K      | 0.09 | _                | 0.20 |  |  |  |  |  |  |

| α      | 0°   | _                | 7°   |  |  |  |  |  |  |

Rev. 1.30 23 August 26, 2022

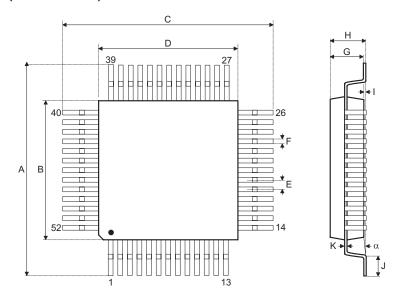

# 52-pin LQFP (14mm×14mm) Outline Dimensions

| Symbol |       | Dimensions in inch |       |  |

|--------|-------|--------------------|-------|--|

| Symbol | Min.  | Nom.               | Max.  |  |

| A      | 0.622 | 0.630              | 0.638 |  |

| В      | 0.547 | 0.551              | 0.555 |  |

| С      | 0.622 | 0.630              | 0.638 |  |

| D      | 0.547 | 0.551              | 0.555 |  |

| Е      | _     | 0.039 BSC          | _     |  |

| F      | 0.015 | _                  | 0.019 |  |

| G      | 0.053 | 0.055              | 0.057 |  |

| Н      | _     | _                  | 0.063 |  |

| I      | 0.002 | _                  | 0.008 |  |

| J      | 0.018 | _                  | 0.030 |  |

| K      | 0.005 | _                  | 0.007 |  |

| α      | 0°    | _                  | 7°    |  |

| Symbol |       | Dimensions in mm |       |  |

|--------|-------|------------------|-------|--|

| Symbol | Min.  | Nom.             | Max.  |  |

| A      | 15.80 | 16.00            | 16.20 |  |

| В      | 13.90 | 14.00            | 14.10 |  |

| С      | 15.80 | 16.00            | 16.20 |  |

| D      | 13.90 | 14.00            | 14.10 |  |

| E      | _     | 1.00 BSC         | _     |  |

| F      | 0.39  | _                | 0.48  |  |

| G      | 1.35  | 1.40             | 1.45  |  |

| Н      | _     | _                | 1.60  |  |

| I      | 0.05  | _                | 0.20  |  |

| J      | 0.45  | _                | 0.75  |  |

| K      | 0.13  | _                | 0.18  |  |

| α      | 0°    | _                | 7°    |  |

Rev. 1.30 24 August 26, 2022

Copyright<sup>©</sup> 2022 by HOLTEK SEMICONDUCTOR INC. All Rights Reserved.

The information provided in this document has been produced with reasonable care and attention before publication, however, HOLTEK does not guarantee that the information is completely accurate. The information contained in this publication is provided for reference only and may be superseded by updates. HOLTEK disclaims any expressed, implied or statutory warranties, including but not limited to suitability for commercialization, satisfactory quality, specifications, characteristics, functions, fitness for a particular purpose, and non-infringement of any third-party's rights. HOLTEK disclaims all liability arising from the information and its application. In addition, HOLTEK does not recommend the use of HOLTEK' products where there is a risk of personal hazard due to malfunction or other reasons. HOLTEK hereby declares that it does not authorise the use of these products in life-saving, life-sustaining or safety critical components. Any use of HOLTEK' products in life-saving/sustaining or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold HOLTEK harmless from any damages, claims, suits, or expenses resulting from such use. The information provided in this document, including but not limited to the content, data, examples, materials, graphs, and trademarks, is the intellectual property of HOLTEK (and its licensors, where applicable) and is protected by copyright law and other intellectual property laws. No license, express or implied, to any intellectual property right, is granted by HOLTEK herein. HOLTEK reserves the right to revise the information described in the document at any time without prior notice. For the latest information, please contact us.

Rev. 1.30 25 August 26, 2022