### SENSYLINK Microelectronics

# (CA9539) Low Voltage 16-bit PC and SMBus I/O Expander with Interrupt

CA9539 is a 16-bit remote GPIO expander. It provides remote GPIO expansion for most MCU families via the I<sup>2</sup>C or SMBus interface.

It is ideally used in Server and Telecom equipment.

### **Table of Contents**

| 1 Description                                          | 4  |

|--------------------------------------------------------|----|

| 2 Features                                             |    |

| 3 Applications                                         | 4  |

| 4 PIN Configurations (Top View)                        | 4  |

| 5 Typical Application                                  |    |

| 6 Pin Description                                      |    |

| 7 Function Block                                       | 7  |

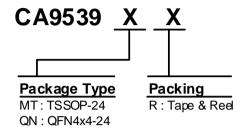

| 8 Ordering Information                                 | 8  |

| 9 Specification                                        |    |

| 9.1 Absolute Maximum Ratings                           | 9  |

| 9.2 Recommended Operating Conditions                   | 9  |

| 9.3 Electrical Characteristics                         |    |

| 9.4 RESET Timing Characteristics                       | 11 |

| 9.5 Switching Characteristics                          | 12 |

| 9.6 I <sup>2</sup> C Interface Timing Requirements     | 12 |

| 10 Function Descriptions                               | 14 |

| 10.1 Device address                                    |    |

| 10.2 Registers                                         |    |

| 10.2.1 Command byte                                    |    |

| 10.2.2 Registers 0 and 1: Input port registers         |    |

| 10.2.3 Registers 2 and 3: Output port registers        |    |

| 10.2.4 Registers 4 and 5: Polarity Inversion registers |    |

| 10.2.5 Registers 6 and 7: Configuration registers      |    |

| 10.3 Power-on reset                                    |    |

| 10.4 RESET input                                       |    |

| 10.5 Interrupt output                                  |    |

| 10.6 I/O port                                          |    |

| 11 Bus transactions                                    |    |

| 11.1 Writing to the port registers                     |    |

| 11.2 Reading the port registers                        |    |

| 11.3 Characteristics of the I <sup>2</sup> C-bus       |    |

| 11.3.1 Bit transfer                                    |    |

| 11.3.2 START and STOP conditions                       |    |

| 11.3.3 System configuration                            |    |

| 11.3.4 Acknowledge                                     |    |

| 12 Package Outline Dimensions and Layout Information   |    |

| 12.1 (TSSOP-24)                                        |    |

| 12.2 (1550P-24)                                        |    |

| 13 Packing information                                 |    |

| 17 INEVIOLUTI HISTORY                                  |    |

# Figures and Tables

| Figure 1. Typical Application of CA9539                        | 5  |

|----------------------------------------------------------------|----|

| Figure 2. CA9539 function block                                | 7  |

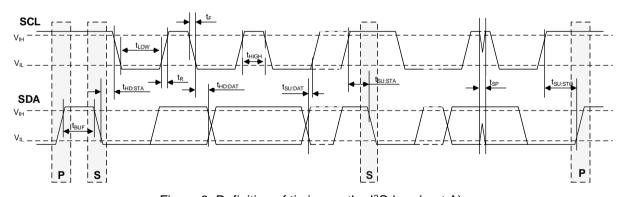

| Figure 3. Definition of timing on the I2C-bus (part A)         | 13 |

| Figure 4. Definition of timing on the I2C-bus (part B)         |    |

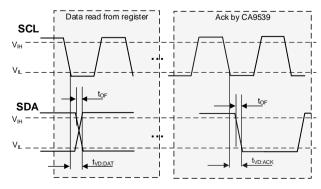

| Figure 5. CA9539 device address                                |    |

| Figure 6. Reset Load Circuits and Voltage Waveforms            | 16 |

| Figure 7. Simplified schematic of I/Os                         |    |

| Figure 8. Write to Output port registers                       |    |

| Figure 9. Write to Configuration registers                     |    |

| Figure 10. Read from register                                  |    |

| Figure 11. Read input port register                            |    |

| Figure 12. Bit transfer                                        |    |

| Figure 13. Definition of START and STOP conditions             |    |

| Figure 14. System configuration                                |    |

| Figure 15. Acknowledgement on the I <sup>2</sup> C-bus         | 23 |

|                                                                |    |

| Table 1. Pin Description                                       | 6  |

| Table 2. Command byte                                          |    |

| Table 3. Input port 0 Register (register 0, 0x00)              | 15 |

| Table 4. Input port 1 Register (register 1, 0x01)              | 15 |

| Table 5. Output port 0 Register (register 2, 0x02)             | 15 |

| Table 6. Output port 1 Register (register 3, 0x03)             | 15 |

| Table 7. Polarity Inversion port 0 register (register 4, 0x04) | 15 |

| Table 8. Polarity Inversion port 1 register (register 5, 0x05) |    |

| Table 9. Configuration port 0 register (register 6, 0x06)      | 16 |

| Table 10. Configuration port 1 register (register 7, 0x07)     |    |

### 1 Description

The chip is a 16-bit I/O expander. It provides remote GPIO expansion for most MCU families via the I<sup>2</sup>C or SMBus interface. The CA9539 has two 8-bit Input Port register, Output Port register, Configuration register (setup as input or output), and Polarity Inversion register (active high or active low). After power on, the 16 I/O pins are configured as inputs. However, the master can enable the I/O pins as either inputs or outputs individually by setup the configuration register bits. The data for each input or output is stored in the corresponding input or output port register. The polarity of the Input Port register can be inverted with the Polarity Inversion register.

The master can reset the chip probably caused by timeout or other improper operation using the power-on reset feature, which resets all registers in their default state and initializes the I<sup>2</sup>C/SMBus state machine. The chip has outputs latch feature, which can protect the chip when driving LEDs directly with high-current capability.

The CA9539 open-drain interrupt output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. The chip can be reset to its default state by cycling the power supply and causing a power-on-reset or applying logic low to  $\overline{\text{RESET}}$  pin.

Available Package: TSSOP-24, QFN4x4-24 package.

#### 2 Features

- Operation Voltage: 1.65V to 5.5V

- Low Standby Current

- 5.5V Tolerance I/O Port

- Remote 16-bit GPIO Expander

- Compatible with SMBus and I<sup>2</sup>C interface

- I<sup>2</sup>C Speed up to 1.0MHz (Fast-mode Plus)

- Up to 4 slave addresses

- Open-drain Interrupt output with active low to indicate input state changed.

- Input, Output, and Configuration Register

- Polarity Inversion Register

- Built-in Power-on Reset

- No Glitch during Power-up

- Noise Filter on SCL/SDA inputs

- 16 I/O pins

- As Input without pull-up resistor (default)

- As Output with internal push-pull

- Latch feature when driving LEDs directly with high current capability

- Temperature Range: -40°C to 85°C

### 3 Applications

- Server, Notebook PC

- Telecom equipment

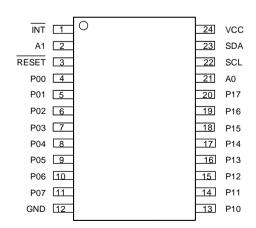

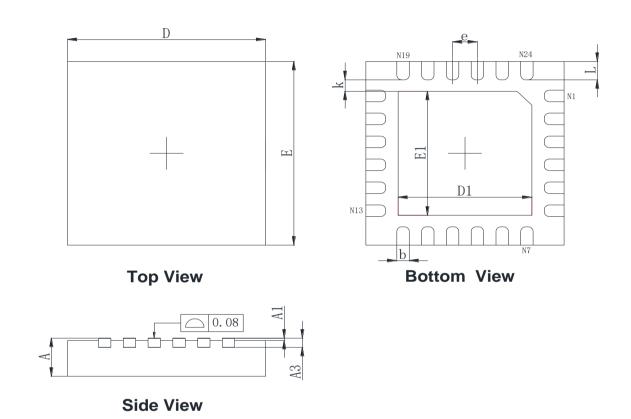

### 4 PIN Configurations (Top View)

TSSOP-24 (Package Code MT)

QFN4x4-24(Package Code QN)

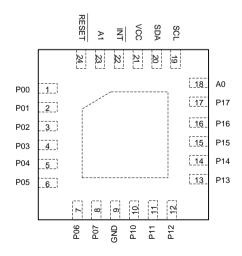

# 5 Typical Application

- A. Device address configured as 1110 100xb for this example.

- B. P00,P02, P03 configured as outputs.

- C. P01 and P04-P17 configured as inputs.

- $\ensuremath{\mathsf{D}}.$  Pin numbers show are for the MT package.

Figure 1. Typical Application of CA9539

# **6 Pin Description**

Table 1. Pin Description

| PIN No.  |          | l No.     |                                                                                                                                                              |

|----------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN Name | TSSOP-24 | QFN4x4-24 | Description                                                                                                                                                  |

| ĪNT      | 1        | 22        | Interrupt open-drain output with active low. Connect to Vcc through a pull-up resistor                                                                       |

| A1       | 2        | 23        | Slave addresses setup pin1, combined with A0, which can generate 4 kinds of slave addresses by connecting these pins to GND or V <sub>CC</sub> respectively. |

| RESET    | 3        | 24        | Reset input pin with active low. Connect to $V_{\text{CC}}$ through a pull-up resistor if no active connection is used                                       |

| P00      | 4        | 1         | GPIO bit0 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P01      | 5        | 2         | GPIO bit1 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P02      | 6        | 3         | GPIO bit2 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P03      | 7        | 4         | GPIO bit3 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P04      | 8        | 5         | GPIO bit4 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P05      | 9        | 6         | GPIO bit5 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P06      | 10       | 7         | GPIO bit6 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| P07      | 11       | 8         | GPIO bit7 of Port0, input/output: push-pull structure; default as input after power on.                                                                      |

| GND      | 12       | 9         | Ground pin.                                                                                                                                                  |

| P10      | 13       | 10        | GPIO bit0 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P11      | 14       | 11        | GPIO bit1 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P12      | 15       | 12        | GPIO bit2 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P13      | 16       | 13        | GPIO bit3 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P14      | 17       | 14        | GPIO bit4 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P15      | 18       | 15        | GPIO bit5 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P16      | 19       | 16        | GPIO bit6 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| P17      | 20       | 17        | GPIO bit7 of Port1, input/output: push-pull structure; default as input after power on.                                                                      |

| A0       | 21       | 18        | Slave addresses setup pin0, combined with A1, which can generate 4 kinds of slave addresses by connecting these pins to GND or Vcc respectively.             |

| SCL      | 22       | 19        | Digital interface clock input pin, need a pull-up resistor to Vcc.                                                                                           |

| SDA      | 23       | 20        | Digital interface data input or output pin, need a pull-up resistor to Vcc.                                                                                  |

| Vcc      | 24       | 21        | Power supply input pin, using 0.1uF low ESR ceramic capacitor to ground                                                                                      |

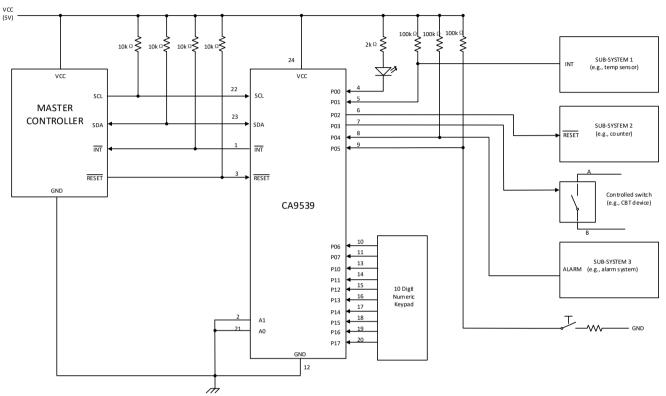

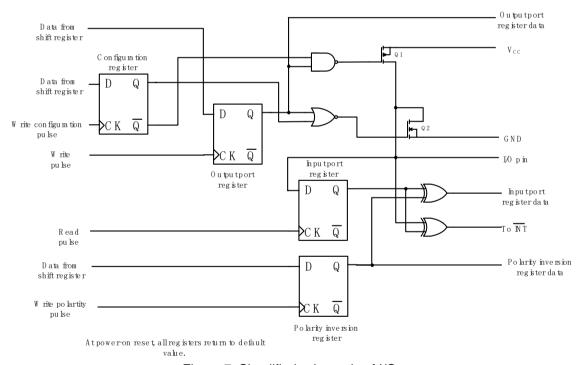

### 7 Function Block

Figure 2. CA9539 function block

# **8 Ordering Information**

| Order PN  | Green <sup>1</sup> | Package   | Marking ID <sup>2</sup> | Packing     | MPQ   | Operation<br>Temperature |

|-----------|--------------------|-----------|-------------------------|-------------|-------|--------------------------|

| CA9539MTR | Halogen free       | TSSOP-24  | 9539<br>YWWAXX          | Tape & Reel | 4,000 | -40°C ~ +85°C            |

| CA9539QNR | Halogen free       | QFN4x4-24 | 9539<br>YWWAXX          | Tape & Reel | 5,000 | -40°C ~ +85°C            |

#### Notes

1. Sensylink can meet RoHS 2.0/REACH requirement. So most package types Sensylink offers only states halogen free, instead of lead free.

<sup>2.</sup> Marking ID includes 2 rows of characters. In general, the 1<sup>st</sup> row of characters are part number, and the 2<sup>nd</sup> row of characters are date code plus production information.

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

### 9 Specification

#### 9.1 Absolute Maximum Ratings

| Parameter                                | Symbol                                                         | Value      | Unit |

|------------------------------------------|----------------------------------------------------------------|------------|------|

| Supply Voltage                           | Vcc to GND                                                     | -0.5 to 6  | V    |

| SDA, SCL, P00-P17 Voltage                | V <sub>SDA</sub> /V <sub>SCL</sub> /V <sub>P00-17</sub> to GND | -0.5 to 6  | V    |

| A0, A1 Voltage                           | V <sub>A0</sub> /V <sub>A1</sub> to GND                        | -0.5 to 6  | V    |

| INT, RESET Voltage                       | VINT, VRESET tO GND                                            | -0.5 to 6  | V    |

| P00-P17 Output Current                   |                                                                | ±50        | mA   |

| Storage temperature Range                | T <sub>STG</sub>                                               | -65 to 150 | °C   |

| Lead Temperature (Soldering, 10 Seconds) | TLEAD                                                          | 260        | °C   |

| ESD MM                                   | ESD <sub>MM</sub>                                              | ±400       | ٧    |

| ESD HBM                                  | ESD <sub>HBM</sub>                                             | ±4000      | V    |

| ESD CDM                                  | ESD <sub>CDM</sub>                                             | ±1000      | V    |

Note

#### 9.2 Recommended Operating Conditions

| Parameter                              | Symbol         | Condition                                 | MIN     | MAX                 | Unit |

|----------------------------------------|----------------|-------------------------------------------|---------|---------------------|------|

| Supply Voltage                         | Vcc            |                                           | 1.65    | 5.5                 | V    |

| High level innut valtage               |                | SCL, SDA                                  | 0.7×Vcc | Vcc                 | V    |

| High-level input voltage               | ViH            | A1–A0, P07–P00, P17–P10                   | 0.7×Vcc | 5.5                 | V    |

|                                        |                | SCL, SDA                                  | -0.5    | 0.3×Vcc             | V    |

| Low-level input voltage                | VIL            | A1–A0, RESET, P07–P00,<br>P17–P10         | -0.5    | 0.3×V <sub>CC</sub> | V    |

| High-level output current              | Іон            | P07–P00, P17–P10                          |         | -10                 | mA   |

| Low-level output current               | loL            | V <sub>OL</sub> =0.4V<br>P07–P00, P17–P10 |         | 11                  | mA   |

| Low level output current               |                | $V_{OL}$ =0.4V, $\overline{INT}$ , SDA    |         | 3.5                 | mA   |

| Ambient Operation<br>Temperature Range | T <sub>A</sub> |                                           |         | -40 ~ +85           | °C   |

Note

<sup>1)</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at the "Absolute Maximum Ratings" conditions or any other conditions beyond those indicated under "Recommended Operating Conditions" is not recommended. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

<sup>(1)</sup> For voltage applied above VCC, an increase in ICC will result.

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

#### 9.3 Electrical Characteristics

Test Conditions:  $C_{IN} = 0.1 uF$ ,  $V_{CC} = 1.65 V$  to 5.5V,  $T_A = -40$  to 85°C unless otherwise specified.

| Parameter                               | Symbol           | TEST CONDITIONS                                                                                              | MIN     | TYP (1) | MAX                 | UNIT |

|-----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------|---------|---------|---------------------|------|

| Supply Voltage                          | Vcc              |                                                                                                              | 1.65    |         | 5.5                 | V    |

|                                         |                  | $V_{CC}$ = 5.5 V; no load; $f_{SCL}$ = 400 kHz $V_{I}$ = $V_{CC}$ or GND                                     |         | 35      | 50                  | uA   |

| Supply Current                          |                  | Vcc = 3.6 V; no load;fscL = 400 kHz<br>V <sub>I</sub> =Vcc or GND                                            |         | 20      | 30                  | uA   |

| Supply Current                          | Icc              | $V_{CC} = 2.7 \text{ V}$ ; no load; $f_{SCL} = 400 \text{ kHz}$<br>$V_{I} = V_{CC} \text{ or GND}$           |         | 13      | 19                  | uA   |

| Standby current  Power-on reset voltage |                  | $V_{CC} = 1.65V$ ;no load; $f_{SCL} = 400 \text{ kHz}$<br>$V_I = V_{CC}$ or GND                              |         | 8       | 11                  | uA   |

|                                         |                  | $V_{CC} = 5.5 \text{ V}$ ; no load; $f_{SCL} = 0 \text{ kHz}$ ; $V_1 = V_{CC}$ ; $I/O = \text{inputs}$       |         | 1.3     | 4.2                 | uA   |

|                                         |                  | $V_{CC}$ = 3.6 V; no load; $f_{SCL}$ = 0 kHz; $V_1$ = $V_{CC}$ ; $I/O$ = inputs                              |         | 0.9     | 2.5                 | uA   |

|                                         |                  | $V_{CC} = 2.7 \text{ V}$ ; no load; $f_{SCL} = 0 \text{ kHz}$ ; $V_I = V_{CC}$ ; $I/O = \text{inputs}$       |         | 0.5     | 2.0                 | uA   |

| Standby current                         | lorp             | $V_{CC}$ = 1.65 V; no load; $f_{SCL}$ = 0 kHz; $V_{I}$ = $V_{CC}$ ; I/O = inputs                             |         | 0.3     | 1.8                 | uA   |

| Starioby current                        | Іѕтв             | $V_{CC} = 5.5 \text{ V}$ ; no load; $f_{SCL} = 0 \text{ kHz}$ ; $V_{I} = \text{GND}$ ; $I/O = \text{inputs}$ |         | 1.5     | 4.5                 | uA   |

|                                         |                  | $V_{CC} = 3.6 \text{ V}$ ; no load; $f_{SCL} = 0 \text{ kHz}$ ; $V_I = \text{GND}$ ; $I/O = \text{inputs}$   |         | 1.2     | 2.8                 | uA   |

|                                         |                  | $V_{CC} = 2.7 \text{ V}$ ; no load; $f_{SCL} = 0 \text{ kHz}$ ; $V_{I} = \text{GND}$ ; $I/O = \text{inputs}$ |         | 0.9     | 2.3                 | uA   |

|                                         |                  | $V_{CC}$ = 1.65 V; no load; $f_{SCL}$ = 0 kHz; $V_{I}$ = GND; I/O = inputs                                   |         | 0.6     | 2.0                 | uA   |

|                                         | V <sub>POR</sub> | no load; VI = Vcc or GND                                                                                     |         | 1.4     | 1.55                | V    |

| High-level input                        | V <sub>IH</sub>  | SCL, SDA                                                                                                     | 0.7×Vcc |         | Vcc (2)             | V    |

| voltage                                 | VIH              | A1–A0, RESET, P07–P00, P17–P10                                                                               | 0.7×Vcc |         | 5.5                 | V    |

| Low-level input                         | VIL              | SCL, SDA                                                                                                     | -0.5    |         | 0.3×Vcc             | V    |

| voltage                                 | VIL              | A1–A0, RESET, P07–P00, P17–P10                                                                               | -0.5    |         | 0.3×V <sub>CC</sub> | V    |

|                                         |                  | $I_{OH} = -8 \text{ mA}; V_{CC} = 1.65 \text{ V}$                                                            | 1.2     |         |                     | V    |

|                                         |                  | Iон = -10 mA; Vcc = 1.65 V                                                                                   | 1.0     |         |                     | V    |

|                                         |                  | Iон = -8 mA; Vcc = 2.3 V                                                                                     | 1.8     |         |                     | V    |

| P-port high-level                       | V <sub>OH</sub>  | I <sub>OH</sub> = -10 mA; V <sub>CC</sub> = 2.3 V                                                            | 1.7     |         |                     | V    |

| output voltage (3)                      | VOH              | $I_{OH} = -8 \text{ mA}; V_{CC} = 3.0 \text{ V}$                                                             | 2.6     |         |                     | V    |

|                                         |                  | Iон = -10 mA; Vcc = 3.0 V                                                                                    | 2.5     |         |                     | V    |

|                                         |                  | $I_{OH} = -8 \text{ mA}; V_{CC} = 4.75 \text{ V}$                                                            | 4.1     |         |                     | V    |

|                                         |                  | Iон = -10 mA; Vcc = 4.75 V                                                                                   | 4.0     |         |                     | V    |

|                                         |                  | SDA V <sub>OL</sub> = 0.4 V                                                                                  | 3       |         |                     | mA   |

| Low-level output                        | la:              | P port (4) V <sub>OL</sub> = 0.5 V                                                                           | 8       |         |                     | mA   |

| current                                 | loL              | P port <sup>(4)</sup> V <sub>OL</sub> = 0.7 V                                                                | 10      |         |                     | mA   |

|                                         |                  | $\overline{\text{INT}} \text{ Vol} = 0.4 \text{ V}$                                                          | 3       |         |                     | mA   |

CA9539

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

#### **Electrical Characteristics (continued)**

| Parameter                  | Symbol | TEST CONDITIONS                                                                                         | MIN | TYP | MAX | UNIT |

|----------------------------|--------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input high leakage current | Іін    | P port; V <sub>I</sub> = V <sub>CC</sub> ; V <sub>CC</sub> = 1.65 V to 5.5 V                            |     |     | 1   | uA   |

| Input low leakage current  | lı∟    | P port; $V_1 = GND$ ; $V_{CC} = 1.65 \text{ V to } 5.5 \text{ V}$                                       |     |     | -1  | uA   |

| Input capacitance          | Ci     | SCL; VI = $V_{CC}$ or GND<br>$V_{CC}$ = 1.65 V to 5.5 V                                                 |     | 3   |     | pF   |

| Input-output pin           | C.     | SDA; VI = V <sub>CC</sub> or GND<br>V <sub>CC</sub> = 1.65 V to 5.5 V                                   |     | 3   |     | pF   |

| capacitance                | Cio    | P port; VI = $V_{CC}$ or GND<br>$V_{CC}$ = 1.65 V to 5.5 V                                              |     | 3.7 |     | pF   |

|                            |        | $V_{CC}$ = 1.65 V to 5.5 V SCL, SDA; VI = $V_{CC}$ or GND                                               |     |     | ±1  | uA   |

| Input leakage current      | lı     | $V_{CC} = 1.65 \text{ V to } 5.5 \text{ V}$<br>A0, A1, $\overline{\text{RESET}}$ ; VI = $V_{CC}$ or GND |     |     | ±1  | uA   |

#### Note:

- (1) All typical values are at nominal supply voltage (1.8-, 2.5-, 3.3-, or 5-V  $V_{CC}$ ) and TA = 25°C.

- (2) For voltages applied above  $V_{CC}$ , an increase in  $I_{CC}$  results.

- (3) Each I/O must be externally limited to a maximum of 25 mA, and each octal (P07–P00 and P17–P10) must be limited to a maximum current of 100 mA, for a device total of 200 mA.

- (4) The total current sourced by all I/Os must be limited to 160 mA (80 mA for P07-P00 and 80 mA for P17-P10).

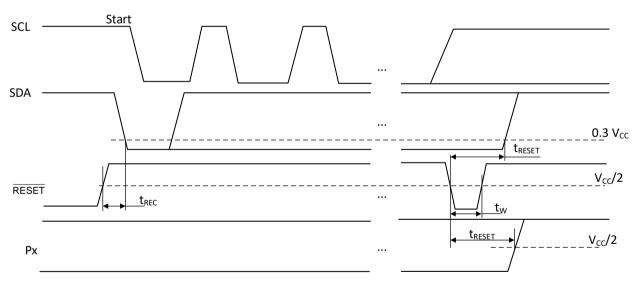

### 9.4 RESET Timing Characteristics

over recommended operating free-air temperature range (unless otherwise noted).

| Parameter            | Symbol | TEST CONDITIONS             | MIN | TYP | MAX | UNIT |

|----------------------|--------|-----------------------------|-----|-----|-----|------|

| Reset pulse duration | tw     |                             | 6   |     |     | ns   |

| Reset recovery time  | trec   |                             | 0   |     |     | ns   |

| Time to reset        | 4      | Vcc=2.3V-5.5V               | 400 |     |     | ns   |

|                      | treset | V <sub>CC</sub> =1.65V-2.3V | 550 |     |     | ns   |

### 9.5 Switching Characteristics

over recommended operating free-air temperature range,  $C_L \le 100 \ pF$  (unless otherwise noted).

| Parameter                                                | Symbol          | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------|-----------------|------------------------------------|-----|-----|-----|------|

| Interrupt valid time                                     | t <sub>iv</sub> | From P port to INT                 |     |     | 4   | us   |

| Interrupt reset delay time                               | t <sub>ir</sub> | From SCL to INT                    |     |     | 4   | us   |

| Output data valid;<br>For Vcc = 2.3 V–5.5 V              |                 | t <sub>pv</sub> From SCL to P port |     |     | 200 | ns   |

| Output data valid;<br>For V <sub>CC</sub> = 1.65 V–2.3 V | <b>ι</b> pv     |                                    |     |     | 300 | ns   |

| Input data setup time                                    | t <sub>ps</sub> | From P port to SCL                 | 150 |     |     | ns   |

| Input data hold time                                     | t <sub>ph</sub> | From P port to SCL                 | 1   |     |     | us   |

### 9.6 I<sup>2</sup>C Interface Timing Requirements

Over recommended operating free-air temperature range (unless otherwise noted).

| Parameter                                                         | Symbol              | TEST CONDITIONS    | MIN  | TYP | MAX  | UNIT |

|-------------------------------------------------------------------|---------------------|--------------------|------|-----|------|------|

|                                                                   |                     | Standard-mode      | 0    |     | 100  | kHz  |

| I <sup>2</sup> C clock frequency                                  | fscL                | Fast-mode (1)      | 0    |     | 400  | kHz  |

|                                                                   |                     | Fast-mode Plus (2) | 0    |     | 1000 | kHz  |

|                                                                   |                     | Standard-mode      | 4.7  |     |      | us   |

| I <sup>2</sup> C bus free time between stop<br>and start          | t <sub>BUF</sub>    | Fast-mode          | 1.3  |     |      | us   |

| and start                                                         |                     | Fast-mode Plus     | 0.5  |     |      | us   |

| 120                                                               |                     | Standard-mode      | 4.0  |     |      | us   |

| I <sup>2</sup> C start or repeated start condition hold           | t <sub>HD:STA</sub> | Fast-mode          | 0.6  |     |      | us   |

| Condition field                                                   |                     | Fast-mode Plus     | 0.26 |     |      | us   |

|                                                                   |                     | Standard-mode      | 4.7  |     |      | us   |

|                                                                   | t <sub>SU:STA</sub> | Fast-mode          | 0.6  |     |      | us   |

| condition setup                                                   |                     | Fast-mode Plus     | 0.26 |     |      | us   |

|                                                                   | t <sub>SU:STO</sub> | Standard-mode      | 4.0  |     |      | us   |

| I <sup>2</sup> C stop condition setup                             |                     | Fast-mode          | 0.6  |     |      | us   |

|                                                                   |                     | Fast-mode Plus     | 0.26 |     |      | us   |

| Valid data time of ACK condition                                  |                     | Standard-mode      |      |     | 3.45 | us   |

| (ACK signal from SCL low to                                       | tvd:ack             | Fast-mode          |      |     | 0.9  | us   |

| Valid data time of ACK condition                                  |                     | Fast-mode Plus     |      |     | 0.45 | us   |

|                                                                   |                     | Standard-mode      | 0    |     |      | us   |

| I <sup>2</sup> C serial-data hold time                            | t <sub>HD:DAT</sub> | Fast-mode          | 0    |     |      | us   |

|                                                                   |                     | Fast-mode Plus     | 0    |     |      | us   |

|                                                                   |                     | Standard-mode      |      |     | 3.45 | us   |

| I <sup>2</sup> C Valid data time<br>(SCL low to SDA output valid) | t <sub>VD:DAT</sub> | Fast-mode          |      |     | 0.9  | us   |

| (GGE low to GB/t Gatput valid)                                    |                     | Fast-mode Plus     |      |     | 0.45 | us   |

|                                                                   |                     | Standard-mode      | 250  |     |      | ns   |

| I <sup>2</sup> C serial-data setup time                           | tsu:dat             | Fast-mode          | 100  |     |      | ns   |

|                                                                   |                     | Fast-mode Plus     | 50   |     |      | ns   |

#### I<sup>2</sup>C Interface Timing Requirements (continued)

| Parameter                                   | Symbol         | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|---------------------------------------------|----------------|-----------------|------|-----|------|------|

|                                             |                | Standard-mode   | 4.7  |     |      | us   |

| I <sup>2</sup> C clock low time             | tLOW           | Fast-mode       | 1.3  |     |      | us   |

|                                             |                | Fast-mode Plus  | 0.5  |     |      | us   |

|                                             |                | Standard-mode   | 4.0  |     |      | us   |

| I <sup>2</sup> C clock high time            | tніgн          | Fast-mode       | 0.6  |     |      | us   |

|                                             |                | Fast-mode Plus  | 0.26 |     |      | us   |

|                                             |                | Standard-mode   |      |     | 300  | ns   |

| I <sup>2</sup> C input fall time            | t⊧             | Fast-mode       |      |     | 300  | ns   |

|                                             |                | Fast-mode Plus  |      |     | 120  | ns   |

| I <sup>2</sup> C output fall time           |                | Standard-mode   |      |     | 300  | ns   |

| (SDA out, 4.7kΩ R <sub>pull</sub> ,10-pF to | tof            | Fast-mode       |      |     | 300  | ns   |

| 400-pF bus)                                 |                | Fast-mode Plus  |      |     | 120  | ns   |

|                                             |                | Standard-mode   |      |     | 1000 | ns   |

| I <sup>2</sup> C input rise time            | t <sub>R</sub> | Fast-mode       |      |     | 300  | ns   |

|                                             |                | Fast-mode Plus  |      |     | 120  | ns   |

|                                             |                | Standard-mode   |      |     | 50   | ns   |

| I <sup>2</sup> C spike time                 | tsp            | Fast-mode       |      |     | 50   | ns   |

|                                             |                | Fast-mode Plus  |      |     | 50   | ns   |

#### Note:

- (1) In Fast-mode, the external pull-up resistance of SDA and SCL is typically 4.7 kOhm.

- (2) In Fast-mode Plus, the external pull-up resistance of SDA and SCL is typically 0.51kOhm.

Figure 3. Definition of timing on the I<sup>2</sup>C-bus (part A)

Figure 4. Definition of timing on the I<sup>2</sup>C-bus (part B)

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

### **10 Function Descriptions**

The CA9539 is a 16-bit I/O expander for the two-line bidirectional bus (I<sup>2</sup>C) is designed for 1.65-V to 5.5-V V<sub>CC</sub> operation. It provides general-purpose remote I/O expansion for most microcontroller families via the I<sup>2</sup>C interface.

The system master can reset the CA9539 in the event of a time-out or other improper operation by asserting a low in the RESET input. The power-on reset puts the registers in their default state and initializes the I<sup>2</sup>C-SMBus state machine. Asserting RESET causes the same reset-initialization to occur without depowering the part.

One of the features of the CA9539, is that the  $\overline{\text{INT}}$  output can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C bus. Thus, the CA9539 can remain a simple slave device.

#### 10.1 Device address

Figure 5. CA9539 device address

A1 and A0 are the hardware address package pins and are held to either HIGH (logic 1) or LOW (logic 0) to assign one of the four possible slave addresses. The last bit of the slave address (R/W) defines the operation (read or write) to be performed. A HIGH (logic 1) selects a read operation, while a LOW (logic 0) selects a write operation.

#### 10.2 Registers

#### 10.2.1 Command byte

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers will be written or read.

Table 2. Command byte

| Command | Access             | Default value     | Description               |

|---------|--------------------|-------------------|---------------------------|

| 0x00    | Read only          | XX <sup>(1)</sup> | Input port 0              |

| 0x01    | Read only          | XX <sup>(1)</sup> | Input port 1              |

| 0x02    | Read or Write      | 0xFF              | Output port 0             |

| 0x03    | Read or Write      | 0xFF              | Output port 1             |

| 0x04    | 0x04 Read or Write |                   | Polarity Inversion port 0 |

| 0x05    | Read or Write      | 0x00              | Polarity Inversion port 1 |

| 0x06    | 0x06 Read or Write |                   | Configuration port 0      |

| 0x07    | Read or Write      | 0xFF              | Configuration port 1      |

Note: (1) The default value 'XX' is determined by the externally applied logic level.

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

#### 10.2.2 Registers 0 and 1: Input port registers

This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to this register have no effect.

The default value 'X' is determined by the externally applied logic level.

Table 3. Input port 0 Register (register 0, 0x00)

|         | •    | • •  | <u> </u> | ,    |      |      |      |      |

|---------|------|------|----------|------|------|------|------|------|

| Bit     | 7    | 6    | 5        | 4    | 3    | 2    | 1    | 0    |

| Symbol  | 10.7 | 10.6 | 10.5     | 10.4 | 10.3 | 10.2 | I0.1 | 10.0 |

| Default | Х    | Х    | Х        | Х    | X    | Х    | Х    | X    |

Table 4. Input port 1 Register (register 1, 0x01)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | l1.7 | I1.6 | I1.5 | l1.4 | I1.3 | I1.2 | l1.1 | I1.0 |

| Default | Х    | Х    | Χ    | Х    | Х    | Х    | Х    | Х    |

#### 10.2.3 Registers 2 and 3: Output port registers

This register is an output-only port. It reflects the outgoing logic levels of the pins defined as outputs by Registers 6 and 7. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 5. Output port 0 Register (register 2, 0x02)

|   | Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---|---------|------|------|------|------|------|------|------|------|

| S | Symbol  | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | 0.00 |

|   | Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 6. Output port 1 Register (register 3, 0x03)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 01.7 | O1.6 | O1.5 | 01.4 | O1.3 | 01.2 | 01.1 | O1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 10.2.4 Registers 4 and 5: Polarity Inversion registers

This register allows the user to invert the polarity of the Input port register data. If a bit in this register is set (written with '1'), the Input port data polarity is inverted. If a bit in this register is cleared (written with a '0'), the Input port data polarity is retained.

Table 7. Polarity Inversion port 0 register (register 4, 0x04)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Table 8. Polarity Inversion port 1 register (register 5, 0x05)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### 10.2.5 Registers 6 and 7: Configuration registers

This register configures the directions of the I/O pins. If a bit in this register is set (written with '1'), the corresponding port pin is enabled as an input with high-impedance output driver. If a bit in this register is cleared (written with '0'), the corresponding port pin is enabled as an output.

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

Table 9. Configuration port 0 register (register 6, 0x06)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 10. Configuration port 1 register (register 7, 0x07)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 10.3 Power-on reset

When power is applied to  $V_{CC}$ , an internal power-on reset holds the CA9539 in a reset condition until  $V_{CC}$  has reached  $V_{POR}$ . At that point, the reset condition is released and the CA9539 registers and SMBus state machine will initialize to their default states. The power-on reset typically completes the reset and enables the part by the time the power supply is above  $V_{POR}$ .

#### 10.4 RESET input

The RESET input can be asserted to initialize the system while keeping the  $V_{CC}$  at its operating level. A reset can be accomplished by holding the  $\overline{RESET}$  pin LOW for a minimum of tw. The CA9539 registers and I<sup>2</sup>C/SMBus state machine are changed to their default state once  $\overline{RESET}$  is LOW (0). When  $\overline{RESET}$  is HIGH (1), the I/O levels at the ports can be changed externally or through the master. This input requires a pull-up resistor to  $V_{CC}$  if no active connection is used.

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All inputs are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_r/t_f \leq$  30 ns.

- C. The outputs are measured one at a time, with one transition per measurement.

- D. I/Os are configured as inputs.

- E. All parameters and waveforms are not applicable to all devices.

Figure 6. Reset Load Circuits and Voltage Waveforms

**CA9539**

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

#### 10.5 Interrupt output

does not match the contents of the Input Port register.

The open-drain interrupt output is activated when one of the port pins changes states and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the Input Port register is read (see Figure 11). A pin configured as an output cannot cause an interrupt. Since each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way around. Remark: Changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin

#### 10.6 I/O port

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a high-impedance input with a weak pull-up to V<sub>CC</sub>. The input voltage may be raised above V<sub>CC</sub> to a maximum of 5.5 V.

If the I/O is configured as an output, then either Q1 or Q2 is on, depending on the state of the Output Port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low-impedance path that exists between the pin and either Vcc or GND.

Figure 7. Simplified schematic of I/Os

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

#### 11 Bus transactions

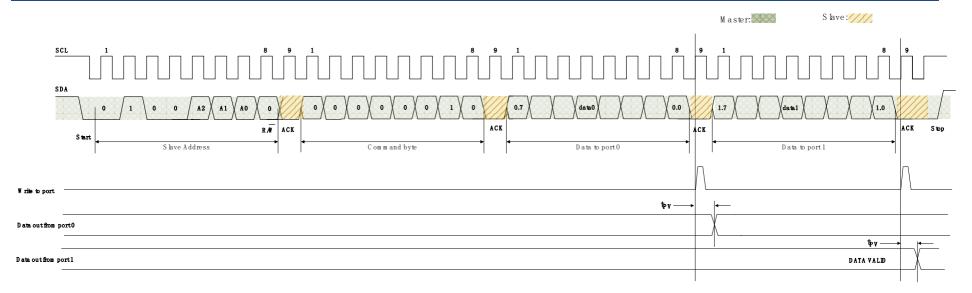

#### 11.1 Writing to the port registers

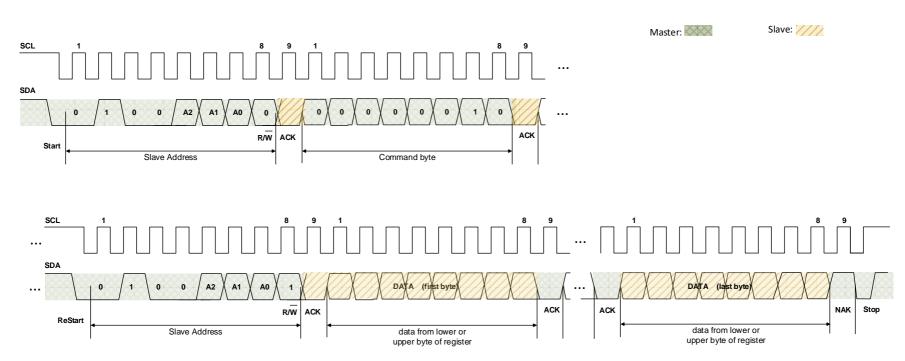

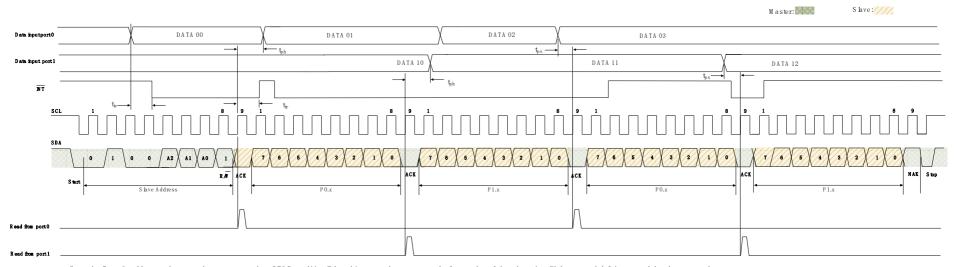

Data is transmitted to the CA9539 by sending the device address and setting the least significant bit to a logic 0 (see Figure 5 "CA9539 device address"). The command byte is sent after the address and determines which register will receive the data following the command byte.

The eight registers within the CA9539 are configured to operate as four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. After sending data to one register, the next data byte will be sent to the other register in the pair (see Figure 8 and Figure 9). For example, if the first byte is sent to Output Port 1 (register 3), then the next byte will be stored in Output Port 0 (register 2).

There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

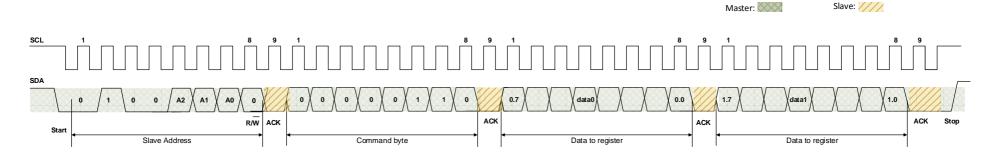

#### 11.2 Reading the port registers

In order to read data from the CA9539, the bus master must first send the CA9539 address with the least significant bit set to a logic 0 (see Figure 5). The command byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again, but this time the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the CA9539 (see Figure 10 and Figure 11). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.

CA9539

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

Figure 8. Write to Output port registers

Figure 9. Write to Configuration registers

CA9539

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

Remark: Transfer can be stopped at any time by a STOP condition.

Figure 10. Read from register

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

Remark: Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknow ledge phase is valid (output mode). It is assumed that the command by the has previously been set to 电小键 each input Portreg is ter).

Figure 11. Read input port register

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

#### 11.3 Characteristics of the I2C-bus

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

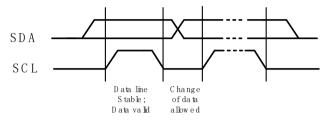

#### 11.3.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Figure 12).

Figure 12. Bit transfer

#### 11.3.2 START and STOP conditions

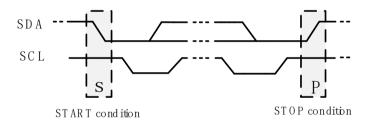

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P) (see Figure 13).

Figure 13. Definition of START and STOP conditions

#### 11.3.3 System configuration

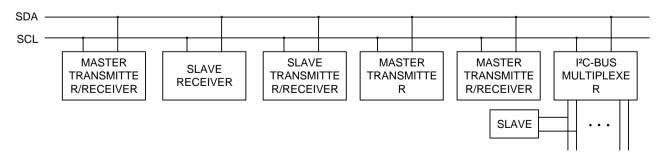

A device generating a message is a 'transmitter'; a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves' (see Figure 14).

Figure 14. System configuration

### Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

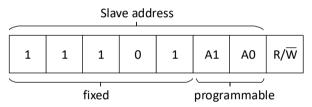

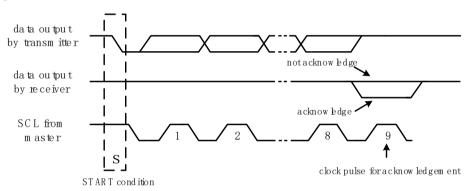

#### 11.3.4 Acknowledge

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up time and hold time must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Figure 15. Acknowledgement on the I<sup>2</sup>C-bus

# 12 Package Outline Dimensions and Layout Information

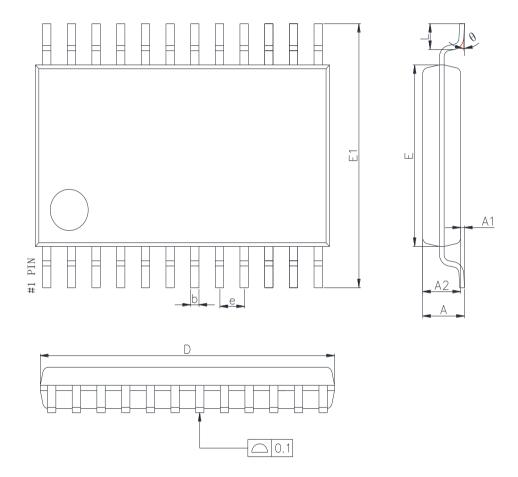

### 12.1 (TSSOP-24)

Package Outline Dimensions (TSSOP-24)

TSSOP-24 Unit (mm)

| Symbol | Dimensions | in Millimeters | Dimension | s in Inches |

|--------|------------|----------------|-----------|-------------|

| Symbol | Min.       | Max.           | Min.      | Max.        |

| Α      |            | 1.200          |           | 0.047       |

| A1     | 0.050      | 0.150          | 0.002     | 0.006       |

| A2     | 0.800      | 1.000          | 0.031     | 0.039       |

| b      | 0.190      | 0.300          | 0.007     | 0.012       |

| С      | 0.090      | 0.200          | 0.004     | 0.008       |

| D      | 7.700      | 7.900          | 0.303     | 0.311       |

| Е      | 4.300      | 4.500          | 0.169     | 0.177       |

| E1     | 6.200      | 6.600          | 0.244     | 0.260       |

| е      | 0.650      | (BSC)          | 0.026 (   | (BSC)       |

| L      | 0.400      | 0.800          | 0.016     | 0.031       |

| θ      | 0°         | 8°             | 0°        | 8°          |

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

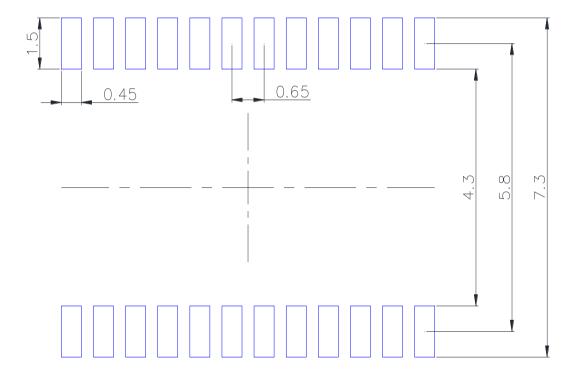

Recommend Land Pattern Layout (TSSOP-24)

TSSOP-24 Unit (mm)

#### Note:

- 1. All dimensions are in millimeter

- 2.Recommend tolerance is within  $\pm 0.1 \text{mm}$

- 3. Change without notice

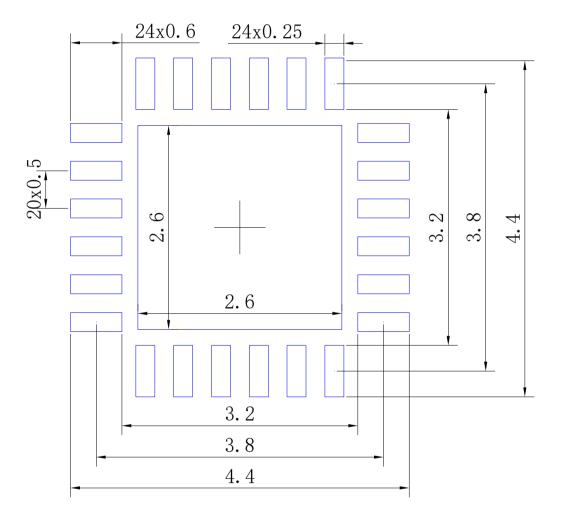

### 12.2 (QFN4x4-24)

Package Outline Dimensions (QFN4x4-24)

QFN4x4-24 Unit (mm)

| Symbol | Dimensions                                      | in Millimeters | Dimension | s in Inches |

|--------|-------------------------------------------------|----------------|-----------|-------------|

| Symbol | Min. 0.700 0.000 3.900 1 2.600 2.600 0.200 0.50 | Max.           | Min.      | Max.        |

| Α      | 0.700                                           | 0.800          | 0.028     | 0.031       |

| A1     | 0.000                                           | 0.050          | 0.000     | 0.002       |

| A3     | 0.203                                           | BREF.          | 0.008     | BREF        |

| D      | 3.900                                           | 4.100          | 0.154     | 0.161       |

| E      | 3.900                                           | 4.100          | 0.154     | 0.161       |

| D1     | 2.600                                           | 2.800          | 0.102     | 0.110       |

| E1     | 2.600                                           | 2.800          | 0.102     | 0.110       |

| k      | 0.200                                           | OMIN.          | 0.008     | BREF        |

| b      | 0.200                                           | 0.300          | 0.008     | 0.012       |

| е      | 0.500                                           | TYP.           | 0.020     | OTYP        |

| L      | 0.300                                           | 0.500          | 0.012     | 0.020       |

Note: pin 1 shape for thermal pad on backside is not limited to bevel, it can be a notch or arch

# Low Voltage 16-bit I<sup>2</sup>C and SMBus I/O Expander with Interrupt

Recommend Land Pattern Layout (QFN4x4-24)

QFN4x4-24 Unit (mm)

#### Note:

- 1. All dimensions are in millimeter

- 2.Recommend tolerance is within  $\pm 0.1 \text{mm}$

- 3. If the thermal pad is not necessary, designer can leave the land pattern area blank

- 4. Change without notice

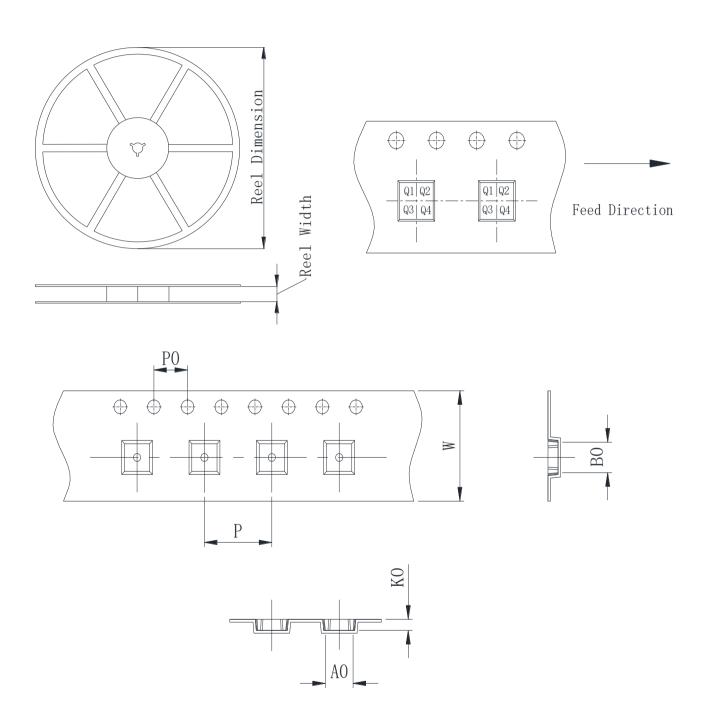

# 13 Packing information

| Package type | Reel<br>size | Reel<br>dimension<br>(±3.0mm) | Reel width (±1.0mm) | A0<br>(±0.1mm) | B0<br>(±0.1mm) | K0<br>(±0.1mm) | P<br>(±0.1mm) | P0<br>(±0.1mm) | W<br>(±0.3mm) | Pin1 |

|--------------|--------------|-------------------------------|---------------------|----------------|----------------|----------------|---------------|----------------|---------------|------|

| TSSOP-24     | 13'          | 330                           | 16.4                | 6.8            | 8.3            | 1.6            | 8.0           | 4.0            | 16.0          | Q1   |

| QFN4x4-24    | 13'          | 330                           | 12.4                | 4.3            | 4.3            | 1.1            | 8.0           | 4.0            | 12.0          | Q2   |

# 14 Revision History

| Version | Date    | Change Content              |

|---------|---------|-----------------------------|

| Ver1.0  | 2020/12 | Initial Version             |

| Ver1.1  | 2021/01 | Update Ordering Information |

| Ver1.2  | 2023/06 | Update Pin Description      |

| Ver1.3  | 2023/09 | Update Icc/Isтв Description |

# SENSYLINK Microelectronics Inc.

www.sensylink.com

#### **IMPORTANT NOTICE**

SENSYLINK Microelectronics Inc. reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein or to discontinue any product or service. Customers should obtain the latest relevant information before placing orders and should verify the latest and complete information. SENSYLINK Microelectronics does not assume any responsibility for use of any product, nor does SENSYLINK Microelectronics any liability arising out of the application or use of this document or any product or circuit described herein. SENSYLINK Microelectronics assumes no liability for applications assistance or the design of Customers' products. Customers are responsible for their products and applications using SENSYLINK Microelectronics components. SENSYLINK Microelectronics does not convey any license under its patent or trademark rights nor the other rights.

SENSYLINK Microelectronics Inc. © 2015 - 2023.